|

k1.spdns.de / Develop / Hardware / K1-Computer / |

| Start | Blog | Project State | K1-CPU | K1-Bus | I/O Boards | Front Panel | Case & PSU | Software |

|

k1.spdns.de / Develop / Hardware / K1-Computer / |

| Start | Blog | Project State | K1-CPU | K1-Bus | I/O Boards | Front Panel | Case & PSU | Software |

Last updated: 2017-09-27

Questions & comments to Kio

Visit my blog on kios-hardware-projects.blogspot.de.

Sometimes you are struck by an idea...

Due to depressions programming became harder and harder. So i thought, why don't do something more simple, with more manual work? Electronics, for instance. And, thanks to the internet, i have already read from other maniacs, who built a 6502 CPU. Or a Z80 in FPGA. Or Dennis Kuschel's myCPU. And there's a web ring about it. If others can do this, it can't be that hard. Basically...

Of course my CPU should be Different. Better. And Simple, so that i can understand it myself. B-)

For symmetry i settled with a 16/16 bit design: 16 data bits and 16 address bits.

• Combined Harvard and Von Neumann architecture

• 16 MHz system clock

Front panel with slow motion clock for exhibitions et. al.

Full static design down to 0 Hz

• 16 bit internal data bus

• 16 bit internal address bus

• 64k x 16 bit internal ram

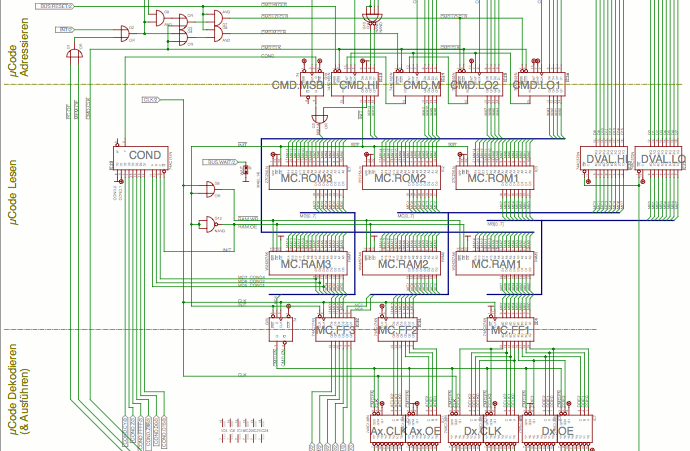

• 32k x 24 bit microcode

organized as 2 code planes à 16k for conditional execution and branching.

the microcode is copied from eproms to rams during boot for increased speed.

it is also possible to load the microcode from an external source instead.

the microcode implements:

boot code, BIOS, kernel

100++ assembler opcodes for ram-based programs

100++ millicode opcodes for microcode-based forth or c-style programs

• No flag register. (but flags)

• Built with discrete logics using 74HCxx and 74ACxx ICs

CPU fits on 5 "Euro" printed circuit boards (160 x 100mm)

• Manual circuit design

Manual routing of the PCBs (with EagleCAD)

Professional made double-layer circuit boards

• 16 bit universal expansion bus

• Up to 16 expansion boards with individual interrupts and priority

• Up to 32 Mbyte/sec data transfer capability

Programs can be written directly in microcode. Adopting this view, the K1 CPU has separated program and data memory. This is the Harvard Architecture.

More likely, the CPU can also use a fixed microcode, which reads opcodes from the ram and executes them. Seen this way it has a combined program and data memory. This is the Von Neumann Architecture.

The microcode is organized in 2 planes of 16k * 24-bit codes. There is a 1-instruction pipeline which imposes a 1-instruction latency on code branching: In every microcode instruction a flag is selected. This flag is tested at the end of the previous instruction and determines from which code plane the next instruction is read. The assembler takes care for the most of this brain hazzard.

All circuit drawings were made with EadleCAD, which is quite affordable.

EagleCAD certainly has it's quirks.

2009-01 Production of the control unit.

2009-02 I'm in the Homebuilt CPU Webring.

2009-03 Working on the microcode and microcode assembler.

2009-09: Manufactured the first version of a front panel.

2009-10: Production of the ALU board.

2009-10-05: CadSoft is bought by Premier Farnell plc.

2009-11: Production of the address register and data register boards.

2009-12: Design of a new new front panel with more 'gears'.

• Subproject LCDs for the front panel.

• Subproject IR-Keyboard for the front panel.

2010-02: Production of the I/O board.

Production of a microcode upload header.

2010-03: Production of the new frontpanel board.

2010-04-05: First Power-On

Power drawn by the CPU is ~350mA@5V when halted and ~800mA@5V when running at 16MHz.

2012-02: Related project: A controller board for an old black&white reflective LCDisplay i own. It is based on an ATMega8 and uses old 41464 DRAM chips for it's frame buffer.

20212-03: Production of IDE and SIO expansion boards.

2012-05: Building a LCD 640x480 pixel b&w LCD terminal.

2012-06: Building 2nd LCD LM64K101 - LCD Display 640x480.

2012-06-27: Started blogging on kios-hardware-projects.blogspot.de.

| Name | Letzte Änderung | Länge | |||

|---|---|---|---|---|---|

| Case+PSU/ | 2019-08-22 19:19 | 5 | |||

| Data Sheets/ | 2019-08-22 19:19 | 37 | |||

| Front Panel/ | 2020-08-29 15:16 | 29 | |||

| Images/ | 2019-08-20 05:21 | 5 | |||

| IO-Boards/ | 2019-08-20 05:21 | 5 | |||

| K1-Bus/ | 2014-04-26 13:14 | 19 | |||

| K1-CPU/ | 2019-08-22 19:19 | 13 | |||

| LM641541 - LCD Display 640x480/ | 2020-08-29 18:14 | 8 | |||

| Software/ | 2020-08-29 18:12 | 7 | |||

| TODO HW.txt | 2010-04-16 16:57 | 305 |

WebRing JavaScript by Qirien Dhaela

To join the Homebuilt CPUs ring, drop Warren a line, mentioning your page's URL. He'll then add it to the list.

You will need to copy the WebRing code fragment into your page. The ring is chartered for projects that include a home-built CPU. It can emulate a commercial part, that's OK. But actually using that commercial CPU doesn't rate. Likewise, the project must have been at least partially built: pure paper designs don't rate either. It can be built using any technology you like, from relays to FPGAs.

powered by vipsi - your friendly VIP Script Interpreter