by Paul Farrow

Third Edition 2013

©2012 by Paul Farrow www.fruitcake.plus.com www.zxresourcecentre.co.uk

**SPECTRA** manual

First published 2012 Second edition 2012 Third edition 2013 ©2012 Paul Farrow

Front cover illustration by John Harris, and used with kind permission.

Prints of his artwork used for the original ZX Spectrum manual covers are available from: www.alisoneldred.com/thumbsJohnHarris-Prints-3-1.html

### **Contents**

#### **CHAPTER 1**

#### Introduction Page 5

A guide to the features provided by the SPECTRA interface.

#### **CHAPTER 2**

#### Setting up the interface Page 9

How to attach the SPECTRA interface to the Spectrum and how to configure its settings.

#### **CHAPTER 3**

#### **SCART connection** Page 15

Describes the SCART connection to a TV, including details on the wiring of the cable required and how to enable sound output. Discusses the purpose of the *video signal absent indicator* LED and how to resolve a detected problem.

#### **CHAPTER 4**

#### New display modes Page 21

Describes the range of new display modes available and how they are generated, and provides details on when you might need to disable them.

#### **CHAPTER 5**

#### Joystick socket Page 43

Describes the pin-out of the joystick socket and how it can be read, and provides details on when you might need to disable it.

#### CHAPTER 6

#### RS232 socket Page 47

Describes the pin-out of the RS232 socket, and includes details on the wiring of a cable suitable for connecting to a PC. Explains how the socket can be controlled from software, and provides details on when you might need to disable it.

#### CHAPTER 7

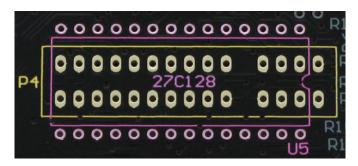

#### ROM support Page 57

Explains how to fit an onboard ROM or add support for ZX Interface 2 ROM cartridges, and discusses the merits and limitations of each option. Describes how to override the Spectrum's ROM or extend it with new BASIC commands.

#### **CHAPTER 8**

#### Reset button and expansion bus Page 65

Explains how to use of the reset button, and describes how the rear expansion bus differs to that exposed by the Spectrum.

#### **APPENDICES**

- A Power usage Page 71

- **B** Hardware compatibility Page 73

- C Troubleshooting Page 75

- **D References** Page 77

## **CHAPTER**

### Introduction

The SPECTRA interface is a multi-purpose peripheral designed for use with a 16K or 48K Spectrum (50 Hz model only). It will not operate with a 128K Spectrum.

The SPECTRA interface provides the following facilities:

- SCART connectivity using RGB to provide a clearer, brighter and better centred picture than that achievable using the standard TV connection.

- Sound output through the television speaker(s).

- New display modes, providing up to 64 colours, increased vertical and horizontal colour resolution, and multiple screen support.

- Kempston compatible joystick socket, with support for auto-fire joysticks.

- ZX Interface 1 compatible RS232 serial port.

- ZX Interface 2 compatible ROM cartridge socket (optional fit).

- Onboard 16K ROM to override or extend the Spectrum's ROM (optional fit).

- Reset button.

- Rear gold plated full width expansion bus.

Note that the ROM cartridge socket and the onboard ROM facilities are mutually exclusive since it is physically only possible to fit one of them.

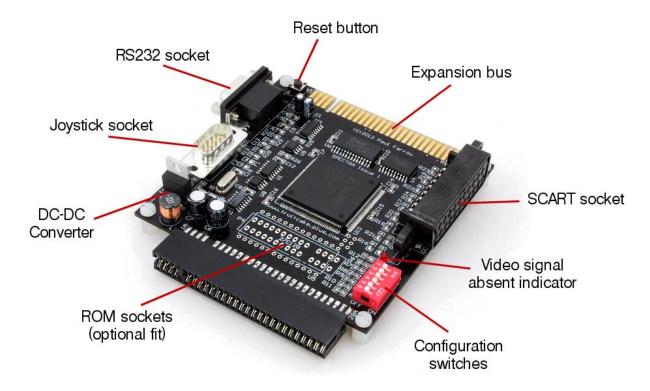

The photograph below identifies the key items found on the SPECTRA interface.

Identification of SPECTRA interface key items

#### Chapter 1

The large square *integrated circuit* (IC) situated at the centre of the board implements the core logic that controls the facilities of the SPECTRA interface. It is a high capacity *complex programmable logic device* (CPLD) and is analogous to the *uncommitted logic array* (ULA) inside the Spectrum.

The interface includes a set of switches that allow specific features to be individually enabled or disabled, thereby achieving maximum compatibility with other interfaces and existing software. By default, the SPECTRA board is shipped with all switches set to the disabled position and hence it initially functions only as a SCART interface.

The *video signal absent indicator* provides visual feedback should the SPECTRA interface detect a problem with the signals used from the Spectrum expansion bus that prevent it from displaying a TV picture via the SCART socket. The indicator, a *light emitting diode* (LED), will shine red if such an error is detected. The condition under which this can occur is described in Chapter 3.

The following items are not included by default with the SPECTRA interface and so must be obtained separately if the corresponding feature is to be used:

- A SCART cable which supports an RGB connection. The vast majority of commercially available SCART cables will be suitable. The wiring of the cable required is described in Chapter 3.

- A 2 x 15-way edge connector socket (if ROM cartridge support is required).

- A 28-way dual-in-line (DIL) IC socket (if an onboard ROM is required).

- A serial cable for use with the RS232 socket. The wiring of the cable required is described in Chapter 6.

In addition, the television must have an RGB enabled SCART socket. There are three different video formats that a SCART socket may support (RGB, composite video and S-video) but often a socket will not support all of these. Televisions which have more than one SCART socket may implement support for a different subset of video formats on each socket, and so all available sockets should be tried until one is found which yields a picture. It is advisable to consult the television instruction manual to determine which of its SCART sockets provide support for connection via RGB.

Throughout the rest of this manual the terms expansion port and expansion bus are used interchangeably to refer to the connection socket located at the rear of the Spectrum and on some peripherals. Likewise, the terms *interface*, *peripheral* and *device* are used interchangeably and refer to a physical board that can be plugged into the Spectrum's expansion port.

# **CHAPTER**

## Setting up the interface

Before handling the SPECTRA interface it is advisable to touch a grounded metal object to ensure you are free of static charge, e.g. external bare metal section of the casing of a plugged in desktop PC. The board should then only be held by its edges to reduce the risk of electrostatic discharge damaging the circuitry.

The SPECTRA interface is mounted on four plastic legs, one per corner of the board. If not already fitted, these must first be attached. Each leg consists of a plastic bolt and a plastic pillar. To attach a leg, push a bolt through a mounting hole from the top side of the board and screw it into a pillar held underneath the board. The bolt can easily be tightened by hand, but a flat bladed screwdriver may be used if preferred.

The SPECTRA interface should be connected to the Spectrum using the following procedure:

- Ensure the television and the Spectrum are both powered off.

- Plug the SPECTRA interface into the Spectrum's expansion port. If you wish to connect other interfaces then the order in which they are connected becomes important (see the section below entitled *Connection order* for details).

- Plug one end of the SCART cable into the SPECTRA interface and the other end into a suitable SCART socket on the television.

- Power on the television.

- Power on the Spectrum.

The SPECTRA interface generates all necessary signalling voltages into the SCART socket to inform the television to automatically display the RGB signal, and so there should be no need to manually select the mode (unless your television does not implement this feature of the SCART specification). It may take a few moments for the television to detect the mode signalling and switch to display the SCART socket input.

The *video signal absent indicator* will light when the SPECTRA interface is powered on but should almost immediately switch off and remain off. The condition under which it may remain on is described in Chapter 3.

#### **Connection order**

The SPECTRA interface can coexist with other peripherals attached to the Spectrum, but the order that these peripherals are connected becomes important if the SPECTRA interface has the onboard ROM or ROM cartridge facility fitted and any of the other peripherals contain their own ROM or support a plug-in ROM. This is because all ROMs must share the same address space and as a result only one may ever be active at a time. If there is only a single ROM based device connected (SPECTRA or other peripheral) then the order of connection is unimportant.

A peripheral wishing exclusive access to the ROM address space can instruct all devices connected in front of it to relinquish control. However, it cannot signal such a

request to devices connected behind it. A peripheral's position within the chain of connected devices therefore sets its access priority to the ROM address space. The highest priority position is at the end of the chain of devices, with priority decreasing the closer to the Spectrum a device gets. The lowest priority ROM is always the one inside the Spectrum. To ensure all connected ROM based devices coexist without conflict, it is necessary to determine the appropriate priority for each of them. This then translates directly into the order that they should be connected behind the Spectrum.

Often the connection order of peripherals is quite apparent. For example, the physical shape of the ZX Interface 1 means it can only be connected directly behind the Spectrum. Likewise, the reduced width expansion bus at the rear of the ZX Interface 2 means that only a ZX Printer can be connected behind it, and so forces the ZX Interface 2 to become the last connected ROM based device (the ZX Printer does not contain a ROM). If a SPECTRA interface were added to a Spectrum system fitted with a ZX Interface 1 and ZX Interface 2 then clearly there is no choice but to connect it in between these two devices.

Another factor limiting the connection order is whether a peripheral provides a rear expansion port. If it does not then it dictates that it must be the last connected device. Although a cheap option for the manufacturer, it can be a frustration to the user who finds it prevents the connection of other devices. The ZX Interface 2 falls into this category, although it does at least provide the ability to connect a ZX Printer behind it. Sinclair imposed this limitation on the ZX Interface 2 purely to keep the cost of its manufacture to a minimum. Ideally, a ROM based device should disable its ROM whenever it detects a peripheral connected behind it is requesting access to the ROM address space. However, to do this requires circuitry, and hence increased cost. Sinclair removed the need for this cost in the ZX Interface 2 by simply ensuring that no other Spectrum peripheral could be connected behind it. Sinclair needed a way to allow a ZX Printer to be connected since it was an official peripheral sold for the Spectrum. It could not be connected ahead of the ZX Interface 2 since it used a smaller width edge connector (having originally been developed for use with the ZX81), but this worked in Sinclair's favour because it allowed the ZX Interface 2 to be equipped with a rear expansion bus only wide enough and only exposing those signals required by the ZX Printer.

Even though a peripheral might provide a rear full width expansion port, it does not necessarily follow that all signals are routed to it and so there may be little choice but to connect the peripheral behind the SPECTRA interface. If modifying the peripheral is acceptable then an alternate solution would be to add the missing connections by soldering wires between the peripheral's edge connector and its expansion bus, thereby allowing the peripheral to be connected in front of the SPECTRA interface.

For ROM based peripherals that do provide a complete rear expansion port, the order they should be connected in depends upon the functionality they provide. ROM based devices fall into three categories:

- 1. The device supplements the Spectrum's BASIC ROM by becoming active when a BASIC error occurs or when particular BASIC commands are executed, e.g. ZX Interface 1, floppy disk interface, Centronics printer interface.

- 2. The device temporarily overrides the Spectrum's ROM when instigated by manual intervention from the user, e.g. pressing the transfer button on a device such as Romantic Robot's Multiface or Datel's Snapshot. Note that the Snapshot interface actually contains an onboard RAM that must be initially loaded with the transfer program from cassette. However, for the purposes of this document any interface that operates using RAM in this manner is still deemed a ROM based device since it operates by overriding the Spectrum's ROM.

- 3. The device permanently overrides the Spectrum's ROM, e.g. the ROM cartridges of the ZX Interface 2.

Typically, these categories form the order in which device types should be connected, i.e. those that supplement the Spectrum's BASIC ROM should be connected first, followed by those that temporarily override the Spectrum's ROM, and finally those that permanently override the Spectrum's ROM. Devices that fall within the same category may generally be connected in any order, unless the instructions for a particular device specifies otherwise.

Note that some ROM based peripherals that provide a full rear expansion port might not monitor for devices connected behind them requesting access to the ROM address space. Such peripherals should be connected at the end of the chain of attached devices, but identifying them could prove a problem since there is no obvious visual indication (a detailed examination of their circuitry is the only way). An example of such a device is the RAM Turbo interface (a ZX Interface 2 clone, providing ROM cartridge and twin joystick sockets).

Another potential problem can occur with devices that provide a Kempston joystick interface but do not fully decode it on input port 31. The RAM Turbo is one such device, which only decodes address line A5 instead of A5, A6 and A7. This causes it to clash with the display mode register provided by the SPECTRA interface (described in Chapter 4). The SPECTRA interface prevents these clashes occurring if such devices are connected behind it (see Chapter 8 for further details).

The SPECTRA interface can support an onboard ROM or a ROM cartridge socket, but if neither of these options has been fitted then the interface can be safely connected anywhere along the chain of devices. When one of these options has been fitted, the SPECTRA interface can be configured to operate as a device of category 1 or 3. Its ROM may be configured to supplement the Spectrum's BASIC ROM, in which case it should be connected towards the front of the chain of attached devices. Or its ROM may be configured to permanently override the Spectrum's ROM just like a ZX Interface 2 ROM cartridge, in which case the SPECTRA interface should be connected towards the end of the chain of attached devices. However, unlike the ZX Interface 2, the SPECTRA interface does monitor for devices connected behind it requesting access to the ROM address space. This allows the SPECTRA interface to

#### Chapter 2

be fitted with a ROM containing a modified version of Spectrum BASIC and for devices that were designed to supplement or interrupt the Spectrum's BASIC ROM to be connected behind it and to operate on the modified version instead, e.g. Multiface, Centronics printer interface. When used in this configuration, the SPECTRA interface should ideally be connected immediately behind the Spectrum, but this may not always be possible, e.g. when a ZX Interface 1 is also connected. In such a case, the ZX Interface 1 would not be able to intercept the ROM fitted on the SPECTRA interface and so its extended BASIC commands would not be available.

#### **Configuration switches**

The SPECTRA interface contains 6 switches that are used to enable / disable the various facilities it provides. The configuration switches are numbered 1 to 6 and perform the following functions:

- 1. Enables sound output through the television's speaker(s).

- 2. Enables an onboard ROM to override the Spectrum's ROM.

- 3. Enables an onboard ROM or ROM cartridge to extend the Spectrum's ROM.

- 4. Enables the RS232 socket.

- 5. Enables the Kempston joystick socket.

- 6. Enables the new display modes.

A facility is disabled when its control switch is set to the *off* position (the slider pushed to the left), and enabled when set to the *on* position (the slider pushed to the right). The use of each switch is described in the chapter that corresponds to the facility it controls. When operating the switches, avoid placing pressure downwards as this can damage them and ultimately prevent them from working reliably.

# **CHAPTER**

### **SCART** connection

The SCART socket provided by the SPECTRA interface connects to a television using a standard SCART cable. It outputs a RGB signal to produce a high quality picture, and allows the Spectrum's sound to be played through the television's speaker(s). It also provides the necessary control voltages required to instruct the television to automatically select the RGB signal of the SCART socket.

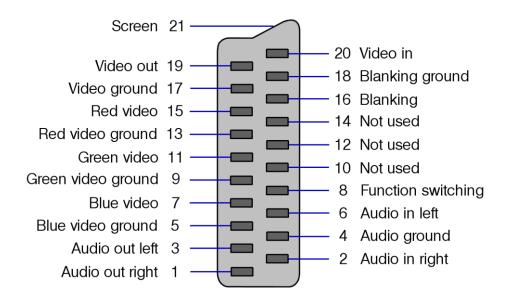

The majority of commercially available SCART cables will be suitable. Alternatively, it is possible to construct your own lead. The diagram below shows the pin-out of the SCART socket provided by the SPECTRA interface.

Front view of the SPECTRA SCART socket

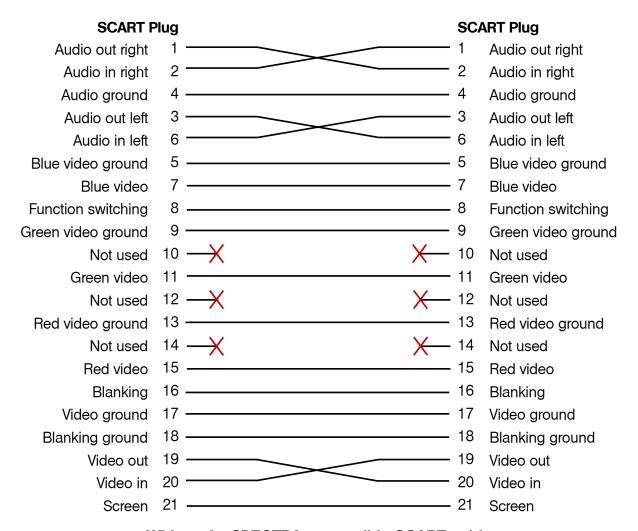

The wiring of a SCART cable suitable for use with the SPECTRA interface is shown on the next page, and results in a cable that can be connected either way round. The ground connections (pins 4, 5, 9, 13, 17 and 18) may be wired individually pin-to-pin between the SCART plugs, or they may all be tied together and linked using a single connection. The cable should be screened to minimise interference.

Modern televisions typically perform processing on an incoming signal to try to improve the quality of the displayed picture, e.g. sharpening, motion smoothing, etc. However, such processing may actually result in a worse picture from the Spectrum and so it may prove beneficial to disable all such filters.

To enable sound output via the television's speaker(s), configuration switch 1 must be set to the *on* position.

Wiring of a SPECTRA compatible SCART cable

#### Video signal absent indicator

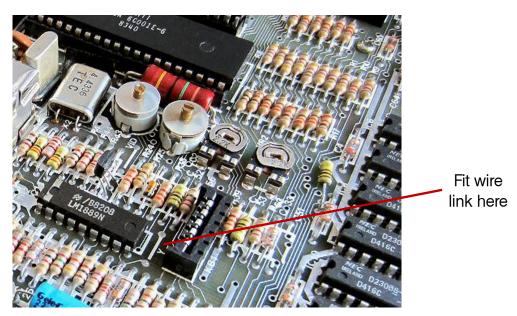

The SPECTRA interface uses the luminance (/Y) signal present on the Spectrum's expansion bus to synchronise the display it outputs from the SCART socket with the standard TV picture generated by the Spectrum. This signal is available by default on the majority of Spectrums, except for issue 1 and early issue 2 machines. In these issue machines, it is taken to the expansion bus via a short wire link but this link is not always fitted. On later builds of the issue 2 Spectrum the link was fitted as standard, and in subsequent issue PCBs the link was removed altogether and replaced with a continuous track. The purpose of the *video signal absent indicator* LED on the SPECTRA interface is to provide a visual indication should the luminance signal not be found. Note that upon powering up the Spectrum, the LED will light but should then switch off almost immediately. If it stays on then it is highly probable that the Spectrum does not have the link fitted and so one must be soldered in.

It is possible to identify an issue 1 or issue 2 Spectrum from a quick visual inspection through the rear expansion port. If a heatsink cannot be seen spanning across the top of the expansion bus then the Spectrum is an issue 1 or issue 2 machine. If there is a daughter board spanning across the expansion bus, then the Spectrum is an issue 1 (the daughter board was used to expand the computer from 16K to 48K, whereas in

all later issues the additional RAM was housed directly onboard the main PCB). If a daughter board is not visible but three thick tracks with about a dozen thinner tracks beyond them running behind the length of the expansion bus can be seen then the Spectrum is an issue 1 (all subsequent models have ICs present here instead).

The location to fit the wire link inside an issue 1 Spectrum is shown in the following photograph:

Luminance wire link position in issue 1 Spectrum

The location to fit the wire link inside an issue 2 Spectrum is shown in the following photograph:

Luminance wire link position in issue 2 Spectrum

In both cases, the wire link should be fitted between the two holes marked with a white line and labelled 'Y'.

## **CHAPTER**

## **New display modes**

Whereas the Spectrum only supports a single limited colour display format, the SPECTRA interface provides support for an additional 31 display formats. These allow up to 64 unique colours to be shown simultaneously, and at a variety of colour resolutions up to eight times higher in the vertical direction and up to two times higher in the horizontal direction than the standard Spectrum display. The additional colours may also be applied to the border area, and the interface includes support for multiple screens (similar in concept to the dual screen mechanism introduced on the Spectrum 128). These new display modes are achieved without the need for any non-standard internal modifications to the Spectrum.

The new display modes concentrate on the colour aspect of the screen because it is the colour abilities of the Spectrum that are arguably in most need of enhancement. This is due to the design Sinclair used that allowed them to create a computer that was capable of producing a 'full colour' screen using less than 7K of RAM. This feat was achieved by cleverly superimposing a coarse colour grid (the attributes file) on top of a finer pixel grid (the display file). This dramatically reduced the amount of RAM required but resulted in the smallest colour entity covering an area of 8 by 8 pixels, causing the infamous *colour clash* effect seen in many Spectrum games. A design that would have allowed each pixel to be individually set to any of the 8 basic colours would have required 18K of RAM, which is 2K more than the total memory initially shipped with the Spectrum!

To understand the remainder of this chapter, it is useful to establish some terminology to describe the structure of a screen display. The active portion of the Spectrum's display consists of 256 pixels in the horizontal direction and 192 pixels in the vertical direction. The horizontal pixels are grouped into blocks of 8 to form 32 *columns*. The vertical pixels are also grouped into blocks of 8 and form 24 *rows*. The Spectrum's display file operates at the pixel level whereas its attributes file operates at the row and column level. Each byte position in the attributes file is referred to as a cell.

The SPECTRA interface provides support for display modes with attribute heights of 1, 2, 4 and 8 pixels, and widths of 4 and 8 pixels. The height modes are referred to as single line, dual line, quad line, and row and yield vertical colour resolutions of 192, 96, 48 and 24 attributes respectively. The width modes are referred to as full cell and half cell and yield horizontal colour resolutions of 32 and 64 attributes respectively. A cell can therefore hold information for either a single attribute (full cell mode) or two attributes (half cell mode). In all display modes the display file resolution remains at 256 x 192 pixels. When referring to just those aspects of the display mode that affect the size and colour range of the attributes file, the term attribute mode is used. The choice of different attribute modes allows a trade-off between the number of colours, colour resolution and the memory used for the display information.

The range of available attribute modes is summarised in the tables below.

| Full cell mode                           | Number of attributes (horizontal x vertical) |                   |                   |                      |  |  |  |  |

|------------------------------------------|----------------------------------------------|-------------------|-------------------|----------------------|--|--|--|--|

| Colouring supported                      | 32 x 24<br>(row)                             | 32 x 48<br>(quad) | 32 x 96<br>(dual) | 32 x 192<br>(single) |  |  |  |  |

| 8 ink, 8 paper, bright, flash            | ✓                                            | ✓                 | ✓                 | ✓                    |  |  |  |  |

| 8 ink, 8 paper, independent flash        | ✓                                            | ✓                 | ✓                 | <b>√</b> ¹           |  |  |  |  |

| 64 ink, 2 paper, flash                   | ✓                                            | ✓                 | ✓                 | ✓                    |  |  |  |  |

| 64 ink, 64 paper, ink flash, paper flash | ✓                                            | ✓                 | ✓                 | √1                   |  |  |  |  |

| Half cell mode                     | Number of attributes (horizontal x vertical) |                   |                   |                      |  |  |  |  |  |

|------------------------------------|----------------------------------------------|-------------------|-------------------|----------------------|--|--|--|--|--|

| Colouring supported                | 64 x 24<br>(row)                             | 64 x 48<br>(quad) | 64 x 96<br>(dual) | 64 x 192<br>(single) |  |  |  |  |  |

| 8 ink, 1 paper, bright, flash      | ✓                                            | ✓                 | ✓                 | ✓                    |  |  |  |  |  |

| 8 ink, 8 paper, independent flash  | ✓                                            | ✓                 | ✓                 | <b>√</b> ¹           |  |  |  |  |  |

| 64 ink, 1 paper, flash             | ✓                                            | ✓                 | ✓                 | ✓                    |  |  |  |  |  |

| 64 ink, 1 paper, independent flash | ✓                                            | ✓                 | ✓                 | √1                   |  |  |  |  |  |

#### Summary of available attribute modes

Note that it is not possible to fully support 64 ink and 64 paper colours at an attributes file resolution of 32 x 192, or to fully support 8 ink and 8 paper colours at an attributes file resolution of 64 x 192. This is because these modes would require 2K more RAM than is available for use by the attributes file. So instead, a composite display is produced that consists of two areas of different resolutions. The details of this hybrid display format and why there is a limit to the size of the attributes file are described later in this chapter.

The new display modes are only available when enabled by setting configuration switch 6 to the *on* position.

#### **RGB** picture generation

The most obvious approach to generating a RGB picture is to try and decode the YUV colour difference signals available from the Spectrum's expansion bus. However, these signals are subject to so much electrical noise that it is impossible to reliably identify all shades of colour produced by the Spectrum. A solution which bypasses the noise is therefore required.

The Spectrum stores its picture display information at the beginning of the lower 16K RAM bank. The SPECTRA interface listens to all writes to this RAM bank and keeps a copy of the data in its own onboard RAM. It then uses this copy to independently generate a TV picture that is identical to the one produced by the Spectrum. By constructing the TV picture directly from raw display bytes, the issue of electrical noise is completely circumvented.

24

<sup>&</sup>lt;sup>1</sup> Due to limited memory availability, this is a hybrid mode consisting of two regions of different line heights.

For the technique to work, the generated picture must be in perfect synchronisation with the standard TV picture to ensure that the SPECTRA interface only reads from its display RAM at the same moments that the ULA reads from the Spectrum's internal display memory. This then avoids the need for the SPECTRA interface to handle contention conditions with the CPU since the ULA will already be performing this task. To achieve synchronisation, the SPECTRA interface aligns its display generation with the interrupt (/INT) and luminance (/Y) signals exposed on the Spectrum's expansion bus, which allow the start of each TV frame and the start of each scan line within a frame to be determined. If the luminance signal is not active on the expansion bus then the SPECTRA interface cannot synchronise with the standard TV picture and so will not attempt to generate a display (resulting in a blank screen). This condition is detected and reported to the user using the *video signal absent indicator* LED, as described in Chapter 3.

The SPECTRA interface controls the operation of fetching raw display bytes from its RAM and processing them to generate the TV picture. However, it does not have to interpret the bytes in the same manner that the Spectrum interprets those from its display RAM. Further, since a complete copy of the lower 16K RAM bank is available, the SPECTRA interface may interpret as much of this RAM as it wishes when constructing the TV display. This forms the basis of how the new display modes are achieved.

A consequence of the shadowing approach used by the SPECTRA interface is that it limits the memory available for the new display modes to 16K, and is because only this amount is contended with the ULA. Of the 16K, the display file always occupies 6K and so the maximum size available for the attributes file is 10K. This is why the SPECTRA interface cannot support an attributes file of resolution of 32 x 192 when using 64 ink and 64 paper colours, or an attributes file of resolution 64 x 192 when using 8 ink and 8 paper colours. Although it is theoretically possible to use more of the 16K to create a higher pixel resolution display (albeit at the expense of reducing the available range of colours and the colour resolution), it was decided to only target the colour deficiencies of the Spectrum in this version of the SPECTRA interface.

Note that there is actually 32K of RAM onboard the SPECTRA interface, which is divided into two banks of 16K. Only one of these banks is ever shadowing the Spectrum's lower 16K RAM bank, as explained later in this chapter.

The SPECTRA interface generates its TV picture using a similar process to that used by the Spectrum's ULA, although it includes additional logic to implement the extra display modes. For a comprehensive description of how the Spectrum generates its TV picture, refer to *The ZX Spectrum ULA* book [1].

The majority of the new attribute modes can only practically be accessed using machine code but a few can be controlled directly from BASIC and these are described later in this chapter. The ROM paging mechanism provided by the SPECTRA interface opens up the possibility to extend Spectrum BASIC with support for most of new attribute modes, and this is explored further in Chapter 7.

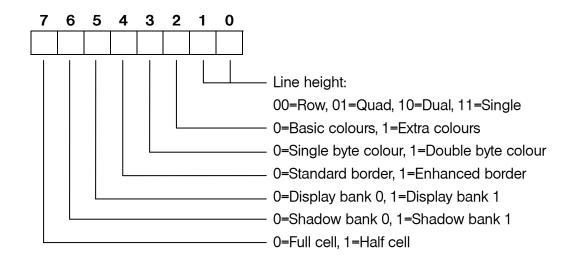

#### Display mode register

The new display modes are selected using an 8-bit register accessed through *input / output* (I/O) port \$7FDF (where \$ denotes the number is in hexadecimal). This register is only accessible when the new display modes have been enabled by setting configuration switch 6 to the *on* position. When enabled, the active display mode is selected by writing to the output port. The port can also be read back, which is useful since it provides a means for a program to determine whether the new display modes functionality is available (the value read back should match the mode previously selected).

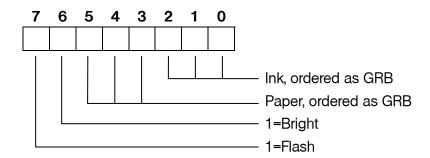

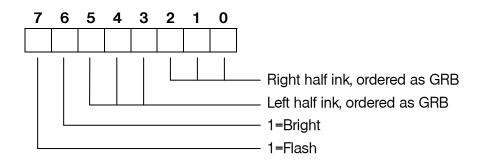

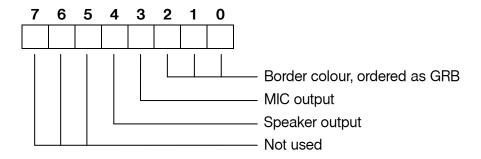

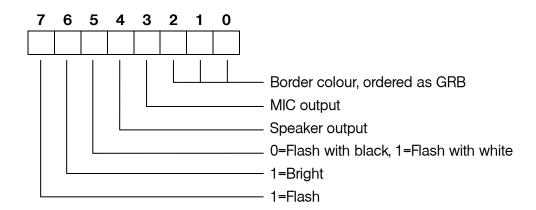

The display mode register is structured as follows:

Each option can be combined with any of the others to form a large range of different display modes.

The *line height* bits are used to select how many pixels form the height of a line, either single line (1 pixel), dual line (2 pixels), quad line (4 pixels) or row (8 pixels).

The *basic / extra colours* bit selects between the conventional range of 15 colours provided by the Spectrum and a larger palette of 64 colours.

The *single / double byte colour* bit selects whether the colour for each attribute position is specified using single bytes or with two bytes. The interpretation of the byte(s) depends upon the *basic / extra colours* bit and the *full / half cell* bit, and determines whether the basic palette of 15 colours is available or the enhanced palette of 64 colours.

The *standard / enhanced border* bit selects between the conventional border functionality offered by the Spectrum and new functionality that allows additional colours to be displayed, including the ability to flash the border.

The *display bank 0 / 1* bit is used to specify which half of the 32K RAM fitted onboard the SPECTRA interface contains the screen information that will be fetched when generating the TV picture. This facility can be used to store a display screen and then

switch back to it when desired. When used with the *shadow bank 0 / 1* bit, a double buffer mechanism is achieved (as described below).

The shadow bank 0 / 1 bit is used to select which half of the 32K RAM fitted onboard the SPECTRA interface will shadow the Spectrum's lower 16K RAM. When used with the display bank 0 / 1 bit, a double buffer mechanism is achieved which allows a program to be constructing a screen image in the shadow bank while the SPECTRA interface is outputting the screen information from the display bank. Once construction of the image has been completed, the roles of the shadow and display banks can be swapped over, thereby producing an instantaneous update on the television without any flicker.

The *full / half cell* bit selects between attributes of 8 pixels wide and 4 pixels wide. The colour byte(s) read in for a cell (as defined by the *single / double byte colour* bit) are interpreted differently for half cell mode than they are for full cell mode. The state of the *basic / extra colours* bit determines whether the basic palette of 15 colours or larger palette of 64 colours is used.

Writing to the display mode register causes an immediate switch to the new configuration. This can result in a visible flicker should the change occur midway through a TV frame. Therefore, it may be desirable to wait until an interrupt occurs before switching to the new mode since this ensures that the change happens prior to the top border being generated. The immediate switch of display modes opens up the possibility to force the construction of a hybrid screen by timing the exact moment that transitions occur between modes.

Note that the standard display mode is always reverted to whenever the reset button is pressed or when configuration switch 6 is set to the *off* position. When either condition happens, the display mode register is loaded with a value of \$00 thereby selecting configuration: row mode, display bank 0, shadow bank 0, standard border, basic colours, single byte colour and full cell mode.

#### Display memory organisation

The standard Spectrum screen memory has the pixel display file located at addresses \$4000 to \$57FF, and the attributes file located at addresses \$5800 to \$5AFF. The ordering of the lines within the display file does not follow a logical progression down the screen but instead follows the distinctive sequence often seen when a loading screen is being read in from cassette. This sequence splits the display into 3 areas of 8 rows, with each area ordered by the pixel line positions within the rows. In contrast, the attributes file is ordered in a logical progression starting from the top row. To understand why the display file uses such an apparently odd layout requires an examination of how each memory location within it is addressed. The diagram that follows shows the addressing schemes for the standard display and attribute files.

|                  | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1            | 0  |

|------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--------------|----|

| Display file:    | 0  | 1  | 0  | A1 | A0 | L2 | L1 | L0 | R2 | R1 | R0 | C4 | C3 | C2 | C1           | C0 |

|                  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |              |    |

| Attributes file: | 0  | 1  | 0  | 1  | 1  | 0  | A1 | A0 | R2 | R1 | R0 | C4 | ဗ  | C2 | <del>C</del> | CO |

The area number is specified by bits An, the row number within an area by bits Rn, the pixel line number within a row by bits Ln and the column number by bits Cn. It can be seen that the lower 8 bits are identical between the display file and the attributes file, and this approach was used since it simplified the picture generation logic inside the ULA. Note that the A0 and A1 bits never both hold a value of 1, and thus the display file and the attributes file can never overlap.

The new attribute modes provided by the SPECTRA interface use an addressing scheme for the display file that is identical to that used by the standard Spectrum screen. However, the addressing schemes used for the various display mode attribute files are different. A relationship between them and the display file can be seen by examining address lines A8 to A12, which shift by one bit position to the left each time the vertical colour resolution is doubled. It becomes clear that although the standard attributes file (row mode) visually appears to be a logical progression, it can actually be thought of as an extreme case of the 'odd' sequence seen in the display file. The addressing schemes for the new attribute modes are shown below.

|                                                                    | 15                                                                 | 14 | 13 | 12 | 11 | 10         | 9  | 8  | 7  | 6  | 5  | 4  | 3   | 2  | 1  | 0  |

|--------------------------------------------------------------------|--------------------------------------------------------------------|----|----|----|----|------------|----|----|----|----|----|----|-----|----|----|----|

| Display file:                                                      | 0                                                                  | 1  | 0  | A1 | A0 | L2         | L1 | LO | R2 | R1 | R0 | C4 | СЗ  | C2 | C1 | C0 |

|                                                                    |                                                                    |    |    |    |    |            |    |    |    |    |    |    |     |    |    |    |

| Row mode:                                                          | 0                                                                  | 1  | 0  | 1  | 1  | D          | A1 | A0 | R2 | R1 | R0 | C4 | C3  | C2 | C1 | C0 |

|                                                                    | ,                                                                  |    |    |    |    |            |    |    |    |    |    |    |     |    |    |    |

| Quad line mode:                                                    | 0                                                                  | 1  | 1  | 0  | D  | A1         | A0 | L2 | R2 | R1 | R0 | C4 | СЗ  | C2 | C1 | C0 |

|                                                                    |                                                                    |    |    | •  | •  |            | •  |    | •  |    |    |    |     |    |    |    |

| Dual line mode:                                                    | 0                                                                  | 1  | 1  | D  | A1 | A0         | L2 | L1 | R2 | R1 | R0 | C4 | СЗ  | C2 | C1 | C0 |

| Single line mode – basic / extra colours using single byte colour: |                                                                    |    |    |    |    |            |    |    |    |    |    |    |     |    |    |    |

|                                                                    | 0                                                                  | 1  | 1  | A1 | A0 | <u>L</u> 2 | L1 | Ŋ  | R2 | R1 | R0 | C4 | СЗ  | C2 | C1 | C0 |

| Single line mode -                                                 | Single line mode – basic / extra colours using double byte colour: |    |    |    |    |            |    |    |    |    |    |    |     |    |    |    |

| Single line area:                                                  | 0                                                                  | 1  | 1  | D  | A0 | L2         | L1 | LO | R2 | R1 | R0 | C4 | င္သ | C2 | C1 | C0 |

|                                                                    | ,                                                                  |    |    |    |    |            |    |    |    |    |    |    |     |    |    |    |

| Dual line area:                                                    | 0                                                                  | 1  | 0  | 1  | 1  | D          | L2 | L1 | R2 | R1 | R0 | C4 | C3  | C2 | C1 | C0 |

The bit denoted by D applies to double byte colour and its action depends upon the full / half cell bit of the display mode register. In full cell mode and in half cell mode

using basic colours, it selects between the ink bytes (when D is 0) and the paper bytes (when D is 1). In half cell mode using extra colours, it selects between the ink bytes for the right half of each cell (when D is 0) and the ink bytes for the left half of each cell (when D is 1). In single byte colour mode, D is always 0.

Single line mode using double byte colour produces a composite screen consisting of two areas of different line resolutions – 128 single pixel height lines followed by 32 double pixel height lines. Both areas support the same colour palette, as specified by the *basic / extra colours* bit of the display mode register.

The size of the attributes file is dictated only by the *line height* and *single / double* byte colour bits of the display mode register. The memory usage for each attribute mode is shown in the following table.

| Line mode | Single byte colour        | Double byte colour             |

|-----------|---------------------------|--------------------------------|

| Row       | \$5800-\$5AFF             | \$5800-\$5AFF                  |

|           | [\$0300]                  | \$5C00-\$5EFF<br>[\$0600]      |

| Quad      | \$6000-\$65FF             | \$6000-\$65FF                  |

|           | [\$0600]                  | \$6800-\$6DFF<br>[\$0C00]      |

|           | [ΦΟΟΟΟ]                   | [\$0000]                       |

| Dual      | \$6000-\$6BFF             | \$6000-\$6BFF<br>\$7000-\$7BFF |

|           | [\$0C00]                  | [\$1800]                       |

| Single    | \$6000-\$77FF<br>[\$1800] | \$5800-\$7FFF<br>[\$2800]      |

Summary of attribute mode memory usage

In double byte colour mode, the attributes file consists of two distinct areas. The first generally holds the ink bytes for each cell and the second holds the paper bytes for each cell (the exception to this is half cell mode with extra colours and using double byte colour, and the format it uses is described later in this chapter). This partitioning comes about because of the addressing schemes used, but has the advantage that it becomes easy to find the corresponding paper byte for an ink byte, and vice versa. It also makes it easy for a program to operate only on the ink or paper bytes instead of having to manipulate both, and this could be exploited to achieve improved performance.

As previously stated, single line mode using double byte colour produces a display that consists of two different line heights. The attributes file spans locations \$5800 to \$7FFF, of which the single line data occupies \$6000 to \$7FFF and the dual line data occupies \$5800 to \$5FFF. Both areas are divided in two, with the first half defining the ink colours and the second half defining the paper colours.

The total number of bytes used by each attribute mode is shown by the number in square brackets, and excludes any unused region in between the two attribute areas. This region, if it exists, is available for use by a program.

In half cell mode with extra colours and using double byte colour, the first half of the attributes file holds the colour for the right half of each cell and the second half of the attributes file holds the colour for the left half for each cell.

#### **Colour byte formats**

The SPECTRA interface drives its SCART socket using 6 colour lines, two for each of the red, green and blue channels. This yields 4 levels for each channel, and they correspond to approximately 0%, 33%, 66% and 100% of full brightness. When the channels are combined, a total of 64 different colours can be produced. Of these 15 match the basic range of colours achievable on the standard Spectrum display. It is the state of the *basic / extra colours* bit of the display mode register that selects whether a basic colour palette or the larger 64 colour palette is used.

The basic colour palette, including each colour's index number and bright variation, is shown below. Note that some attribute modes can only show the non-bright colours due to a lack of resources in the SPECTRA interface to add support for the full range.

**Basic colour palette**

The 64 colour palette, including each colour's index number, is shown below.

| 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  |

|----|----|----|----|----|----|----|----|

| 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

| 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 |

| 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

| 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 |

| 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 |

| 48 | 49 | 50 | 51 | 52 | 53 | 54 | 55 |

| 56 | 57 | 58 | 59 | 60 | 61 | 62 | 63 |

64 colour palette

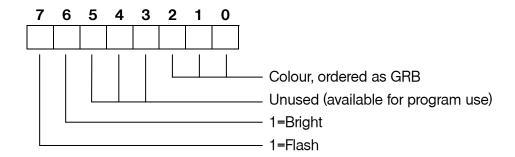

The state of the *single / double byte colour* bit of the display mode register determines whether the ink and paper colour values for an attribute cell are held in

just one byte or separately in two. The interpretation of the attribute byte(s) also depends upon the state of the *full / half cell* bit of the display mode register.

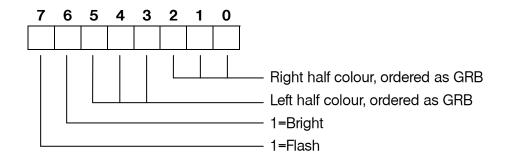

A shorthand notation can be used to specify each attribute mode and consists of the attribute pixel size (width x height) followed by two letters that indicate the colour mode. The attribute width indicates full cell (8 pixels) or half cell (4 pixels) mode, and the attribute height indicates row (8 pixels), quad line (4 pixels), dual line (2 pixels) or single line (1 pixel) mode. The colour mode letters indicate single (S) or double (D) byte colour, and basic (B) or extra (E) colours. The range of attribute modes, along with the interpretation of their attribute byte(s), are summarised below. Each mode is described afterwards in further detail.

| Attribute mode |           |           |           | Attribute cell byte 2                                  | Attribute cell byte 1                                  |  |  |

|----------------|-----------|-----------|-----------|--------------------------------------------------------|--------------------------------------------------------|--|--|

| 8x8<br>SB      | 8x4<br>SB | 8x2<br>SB | 8x1<br>SB |                                                        | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |  |  |

| 8x8<br>DB      | 8x4<br>DB | 8x2<br>DB | 8x1<br>DB | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |  |  |

| 8x8<br>SE      | 8x4<br>SE | 8x2<br>SE | 8x1<br>SE |                                                        | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |  |  |

| 8x8<br>DE      | 8x4<br>DE | 8x2<br>DE | 8x1<br>DE | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |  |  |

| 4x8<br>SB      | 4x4<br>SB | 4x2<br>SB | 4x1<br>SB |                                                        | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |  |  |

| 4x8<br>DB      | 4x4<br>DB | 4x2<br>DB | 4x1<br>DB |                                                        | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |  |  |

| 4x8<br>SE      | 4x4<br>SE | 4x2<br>SE | 4x1<br>SE |                                                        | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |  |  |

| 4x8<br>DE      | 4x4<br>DE | 4x2<br>DE | 4x1<br>DE |                                                        |                                                        |  |  |

The purpose of each bit in the attribute bytes is denoted by labels F, B, I or P to indicate whether it defines flash, bright, ink or paper respectively. Subscripts of I and P indicate that the bit applies only to the ink pixels or only to the paper pixels respectively. Subscripts of L and R indicate that the bit applies only to the left half or only to the right half of the attribute cell respectively. Subscripts of g, r and b indicate the bit specifies the green, red and blue components of the colour respectively. Where two bits appear within an attribute byte for a single colour component, the right most bit defines the least significant bit of the colour. A '–' indicates that the bit is available for use by a program. An '\*' indicates the intended purpose of the bit but due to a lack of resources the SPECTRA interface is unable to support this functionality. In such cases, the bit should always be set to 0 to ensure forwards compatibility with any future version of the SPECTRA interface.

#### Full cell

In basic colours mode using single byte colour, each attribute cell is formatted in the standard Spectrum manner as follows:

The *ink* bits define the colour used for those pixels that are set in the display file, and the *paper* bits define the colour used for those pixels that are reset. Both values are composed of 3 bits, yielding a range of 8 colours for each. When coupled with the *bright* bit a total of 16 different colour values are produced, although only 15 of these are unique since black and bright black display the same. When the *flash* bit is set, the paper and ink colours swap over at a fixed frequency of 1.565 Hz.

In basic colours mode using double byte colour, the first attribute byte defines the ink colour and the second attribute byte defines the paper colour. Both bytes are formatted as follows:

The format encodes the ink and paper using 3 bits each, yielding both a range of 8 colours. The *bright* bit in each byte extends these totals to 16 different colour values, although only 15 of these are unique since black and bright black display the same.

With the *flash* bit in both attribute bytes set, the ink and paper colours swap over at a fixed frequency of 1.565 Hz and replicate the flash mode of the standard Spectrum display. However, if only the ink attribute byte's *flash* bit is set then just the ink coloured pixels swap between the ink colour and the paper colour, and if only the paper attribute byte's *flash* bit is set then just the paper colour pixels swap between the paper colour and the ink colour.

Note that the *unused bits* of each colour byte are available for use as storage by a program. They could, for example, be used in a maze game to hold flags that indicate

which cells contain walls and of what type. If these bits are not used by a program then it is recommended that they always be set to 0.

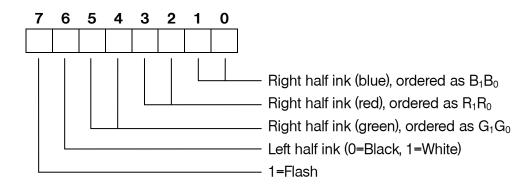

In extra colours mode using single byte colour, each attribute cell is formatted as follows:

The format supports 64 ink colours but only 2 paper colours (black and white). When the *flash* bit is set, the ink and paper colours swap at a fixed frequency of 1.565 Hz.

In extra colours mode using double byte colour, the first attribute cell byte specifies the ink colour and the second attribute cell byte defines the paper colour. Both bytes are formatted as follows:

The format supports 64 colours for the ink and 64 colours for the paper, resulting in a total of  $64 \times 64 = 4096$  different combinations. When the *flash* bits are taken into account, the number of combinations rises to  $4096 \times 2 \times 2 = 16384$ .

With the *flash* bit in both attribute cell bytes set, the ink and paper colours swap over at a fixed frequency of 1.565 Hz. However, if only the ink attribute byte's *flash* bit is set then just the ink coloured pixels swap between the ink colour and the paper colour, and if only the paper attribute byte's *flash* bit is set then just the paper colour pixels swap between the paper colour and the ink colour.

Note that the *unused bit* of each attribute byte is available for use as storage by a program. It is recommended that these bits are always be set to 0 if not used.

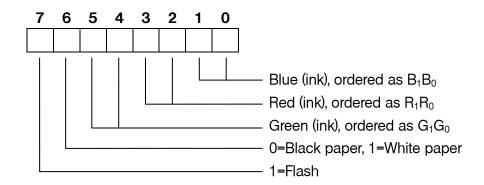

#### Half cell

In basic colours mode using single byte colour, the ink colour for the left and right halves of each cell can be set independently to any of the basic 8 colours. The paper colour is always black. The format of each attribute cell is as follows:

The *bright* bit applies to the full cell and allows a total of 16 different colour values to be produced, although only 15 of these are unique since black and bright black display the same. The *flash* bit applies to the full cell and when set causes the ink colours to swap over with the paper colour at a fixed frequency of 1.565 Hz.

In basic colours mode using double byte colour, the first attribute cell byte defines the ink colour for the two halves of the cell and the second attribute cell byte defines the paper colour for the two halves of the cell. Both bytes are formatted as follows:

The format encodes the left ink, the right ink, the left paper and the right paper using 3 bits, yielding each a range of 8 colours. Both bytes include a *bright* bit, allowing a total of 16 different colour values to be produced for the ink and 16 for the paper, although in each instance only 15 of these are unique since black and bright black display the same. The brightness of the left ink and right ink will always be the same, and likewise the brightness of the left paper and right paper will always be the same.

With the *flash* bit in both attribute cell bytes set, all ink and paper colours in the cell swap over at a fixed frequency of 1.565 Hz. However, if only the ink attribute byte's *flash* bit is set then just the ink coloured pixels in the cell swap between the ink colour and the paper colour, and if only the paper attribute byte's *flash* bit is set then just the paper colour pixels in the cell swap between the paper colour and the ink colour.

In extra colours mode using single byte colour, each attribute cell is formatted as follows:

The format supports 64 ink colours for the right half of the attribute cell but only 2 ink colours for the left half of the attribute cell (black and white). The paper colour is always black. When the *flash* bit is set, the ink and paper colours swap over at a fixed frequency of 1.565 Hz.

In extra colours mode using double byte colour, the first attribute cell byte defines the ink colour for the right half of the cell and the second attribute cell byte defines the ink colour for the left half of the cell. Both bytes are formatted as follows:

The format supports 64 ink colours for both the left and right halves of the attribute cell. Although the format includes a *paper* bit to allow support for two background colours (0=black and 1=white), this is not supported by the SPECTRA interface due to a lack of resources and so only a paper colour of black is available. The bit is therefore marked as *reserved* and should always be set to 0 to ensure compatibility with any future version of the SPECTRA interface.

With the *flash* bit in both attribute cell bytes set, all ink and paper colours in the cell swap over at a fixed frequency of 1.565 Hz. However, if only the first attribute byte's *flash* bit is set then just the right half ink coloured pixels swap between the ink colour and the paper colour, and if only the second attribute byte's *flash* bit is set then just the left half ink coloured pixels swap between the ink colour and the paper colour.

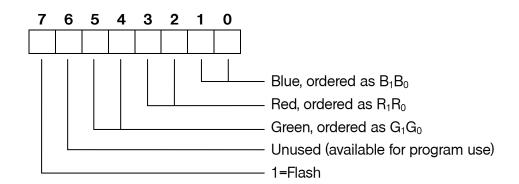

#### Standard / enhanced border

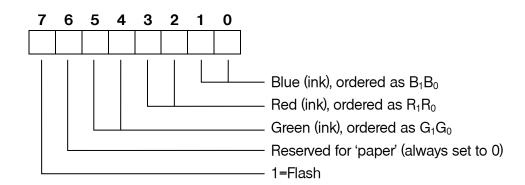

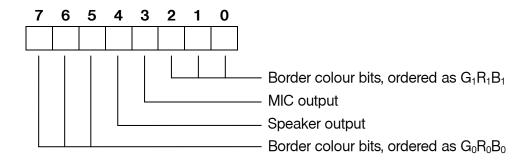

The colour of the border in the standard screen display produced by the Spectrum is set by writing to output port \$FE, and supports just 8 colours. The SPECTRA interface extends the number of supported border colours to 64 by re-interpreting the byte written to output port \$FE when the *standard / enhanced border* bit of the display mode register is set.

In standard border mode, the byte written is interpreted in the usual way as follows:

The mode supports just the basic set of 8 colours available from the Spectrum.

In enhanced border mode, it is the state of the *basic / extra colours* bit in the display mode register that determines how the byte written to output port \$FE is interpreted.

In enhanced border mode using basic colours, the byte written is interpreted as follows:

The *bright* bit is used to increase the intensity of the colour specified by bits 0 to 2, resulting in 16 possible colour values. However, only 15 of these are unique since black and bright black display the same.

When the *flash* bit is set, the border colour alternates at a fixed frequency of 1.565 Hz between the colour specified by bits 0, 1, 2 and 6, and either black (if bit 5 is reset) or white (if bit 5 is set).

Note that the *MIC output* and *speaker output* bits cannot be re-interpreted since they are used by the Spectrum's hardware to control the cassette sockets and the loudspeaker.

In enhanced border mode using extra colours, the byte written to output port \$FE is interpreted as follows:

The two sets of border colour bits are combined to form a 6 bit value, giving a range of 64 unique colours. They are split into high and low order bits to provide a degree of backwards compatibility with standard border mode. Note that there is no facility in this mode to flash the border.

#### Screen bank 0 / 1

As previously described, the SPECTRA interface contains onboard RAM and uses it to shadow the Spectrum's lower 16K RAM bank. The onboard RAM has a capacity of 32K and so is divided into two banks of 16K. The *screen bank 0 / 1* bit selects which bank is read by the SPECTRA interface when generating the TV picture.

The screen bank facility can effectively increase the Spectrum's available memory by off-loading a display from main memory into the inactive screen bank. This display can then be switched to as and when needed. For example, the loading screen for a game could be stored and then re-shown each time the game is over.

The screen bank 0 / 1 bit operates with all available attribute modes. However, it does not affect the border area since this is not stored in the Spectrum's lower 16K RAM bank.

#### Shadow bank 0 / 1

The *shadow bank 0 / 1* bit selects which half of the 32K RAM onboard the SPECTRA interface is shadowing writes to the Spectrum's lower 16K RAM bank.

When the shadow bank and the screen bank point to the same 16K RAM bank, changes to the display and attribute files are immediately reflected to the television.

When the shadow bank and the screen bank point at different 16K RAM banks, a double buffer mechanism is achieved. This allows a program to be constructing one display while another is being shown. Once all drawing has been completed, the roles of the screens can be swapped over to achieve a smooth transition to the new display without any visible appearance of the construction process.

The shadow bank 0 / 1 bit operates with all available attribute modes. However, it does not affect the border area since this is not stored in the Spectrum's lower 16K RAM bank.

### Display mode compatibility

The new display modes provided by the SPECTRA interface are controlled through a specific I/O port, but there is the possibility that this port address might also be used by another peripheral. This could prevent the display mode register from being read, or could cause the other device to become activated when a write to the display mode register occurs. Should such a conflict be encountered, then either the peripheral must be disconnected to allow the new display modes to be used, or the new display modes must be disabled to allow the peripheral to operate correctly.

The new display modes can be disabled by setting configuration switch 6 to the *off* position. This causes the SPECTRA interface to revert to the standard Spectrum display mode and prevents further accesses to the display mode register, thus ensuring full I/O compatibility with 'conflicting' hardware. Further details about the compatibility of the SPECTRA interface with existing hardware and software can be found in Appendix B.

Irrespective of the state of configuration switch 6, the SPECTRA interface will always output a picture through the SCART socket.

### Display mode availability

A program can test whether the new display modes are available by writing a value to the display mode register and then attempting to read it back. If the values do not match then the new display modes are not available. A value of \$FF should be avoided since this is the default value returned if the display modes are not enabled or if a SPECTRA interface is not connected.

Should the value read back be different to that expected (but not \$FF) then another device must have responded to the I/O port read, making it impossible to identify whether the new display modes are available. Note that such a device could also respond with a value of \$FF, thereby giving the impression that no device responded to the I/O port read.

It is also possible that a conflicting device just happens to respond with the expected value, leading to a false detection of the display modes functionality. The chances of this occurring can be significantly reduced by performing the test several times using a variety of different values.

Note that the display mode register uses an I/O port that is contended with the ULA, i.e. it has an address between \$4000 and \$7FFF. This means that the reading of the I/O port will be suspended whilst the ULA is fetching video data from the Spectrum's RAM and will only continue once the ULA has finished its read. As a result, if the display mode register is read when a SPECTRA interface is not connected (or the display modes have been disabled) then a value of \$FF will always be returned. This would not necessarily have been the case if a non-contending I/O port had been used

for the display mode register since then the I/O read would not have been suspended while the ULA performs a memory read. Instead of a value of \$FF being read (the state of an idle data bus), the value returned would have been the display byte being fetched by the ULA. It would only have proved possible to reliably read the display mode register by waiting until an interrupt had occurred since this happens prior to the top border being generated. Using a non-contending I/O port would have made the process of reading the display mode register slower and more involved.

### Display mode control from BASIC

The majority of the new attribute modes can only practically be accessed using machine code, but those that are row based and use single byte colour can be controlled directly from BASIC. In addition, the enhanced border and multiple screen facilities may also be controlled from BASIC. However, it is possible to add support for other attribute modes by extending BASIC using the ROM facilities provided by the SPECTRA interface and this is explored in Chapter 7.

The new display modes that can be directly controlled using standard BASIC are:

- Full cell, row, extra colours, single byte colour mode (8x8 SE).

- Half cell, row, basic colours, single byte colour mode (4x8 SB).

- Half cell, row, extra colours, single byte colour mode (4x8 SE).

- Enhanced border (when in 8x8 SB, 8x8 SE, 4x8 SB or 4x8 SE).

- Multiple screen mechanism (when in 8x8 SB, 8x8 SE, 4x8 SB or 4x8 SE).

The following program demonstrates full cell, row, extra colours, single byte colour mode (8x8 SE) by displaying all colour combinations available:

```

32735,4

10

OUT

FN p(c) = INT (c/8):

DEF

i(c) = c - 8 * FN p(c)

DEF

FΝ

30

FOR

f = Ø

ΤO

40

FOR

P = 0

TO

1

50 FOR n=0

TO

1

TO 63

60 FOR i=0

H f; INVERSE n; BRIGHT p;

INK FN i(i);"a";

70 PRINT FLASH f;

PAPER FN p(i);

80 NEXT i

90 NEXT n

100 NEXT

110 NEXT

```

The ink pixels can be set to any of 64 colours and the paper pixels can be set to black and white only. The program sets the ink pixel colour through the combined use of BASIC commands **INK** and **PAPER**, with **DEF FN** statements being used to simplify the process of translating the 64 palette colour into values to pass to the **INK** and **PAPER** commands. The paper pixel colour is set through the use of the BASIC command **BRIGHT**. The BASIC commands **FLASH** and **INVERSE** operate as usual.

The following program demonstrates half cell, row, basic colours, single byte colour mode (4x8 SB) by displaying all colour combinations available:

```

OUT 32735,128

10

20

FOR

n = 0

TO

7

30

FOR

P = 0

TO

1

40

FOR

f = Ø

TO

50 FOR

1

Ь=0

TO:

60 FOR

i = \emptyset

TO

-7

70 PRINT FLASH f;

BRIGHT b;

INVERSE n;

INK i; "a";

PAPER p;

80 NEXT

i

ь

NEXT

90

100

NEXT

110

NEXT

Р

120 NEXT

```

The ink pixels of the left and right halves of each cell can be set to any of the basic 8 colours, with the paper pixels always being set to black. The program sets the ink pixel colour through the combined use of BASIC commands **INK** and **PAPER**, with the BASIC commands **FLASH**, **BRIGHT** and **INVERSE** operating as usual.

The following program demonstrates half cell, row, extra colours, single byte colour mode (4x8 SE) by displaying all colour combinations available:

```

10 OUT

32735,128+4

DEF

FN p(c) = INT

20

(c/8):

DEF

FΝ

i(c) = c - 8 * FN p(c)

30

FOR

f = Ø

TO

1

40

FOR

P=0

TO

1

50 FOR n=0

TO

i =0

TO 63

60 FOR

70 PRINT FLASH f; BRIGHT p; INVERSE n;

INK FN i (i); "a";

PAPER FN p(i);

i

80 NEXT

NEXT n

90

100 NEXT

110 NEXT

```

The ink pixels of the right half of each cell can be set to any of 64 colours but the ink pixels of the left half of each cell can only be set to black or white. The paper pixels are always set to black. The program sets the ink pixel colour through the combined use of BASIC commands **INK** and **PAPER**, with **DEF FN** statements being used to simplify the process of translating the 64 palette colour into values to pass to the **INK** and **PAPER** commands. The paper pixel colour is set through the use of the BASIC command **BRIGHT**. The BASIC commands **FLASH** and **INVERSE** operate as usual. This mode is probably of limited use due to the left half of each cell only supporting ink colours of black or white.

The enhanced border functionality can be controlled when in any of the row based attribute modes that use single byte colour, i.e. 8x8 SB, 8x8 SE, 4x8 SB and 4x8 SE. The following program demonstrates access to the 64 colour palette when in extra colours mode (8x8 SE).

```

10 OUT 32735,20

20 DEF FN p(c)=INT (c/8):

DEF FN i(c)=c-8*FN p(c):

DEF FN b(c)=32*FN p(c)+FN i(c)

30 FOR c=0 TO 63

40 OUT 254,FN b(c)

50 PAUSE 25

60 NEXT c

70 GO TO 30

```

The program cycles through all available colours. **DEF FN** statements are used to simplify the process of translating the 64 colour palette into a value to output to I/O port 254 (\$FE).

The multiple screen mechanism can be controlled when in any of the row based attribute modes that use single byte colour, i.e. 8x8 SB, 8x8 SE, 4x8 SB and 4x8 SE. It can be used to just store a screen image for display later, or it can be used to implement a double buffer mechanism. The following program demonstrates this latter use and displays screens of random numbers one after the other. To see the effect of screen buffering, uncomment lines 10 and 60. Line 10 selects screen bank 0 for display and screen bank 1 to shadow the Spectrum's lower 16K RAM bank. Line 60 reverses this to select screen bank 1 for display and screen bank 0 to shadow the Spectrum's lower 16K RAM bank.

```

10

REM OUT 32735,64

20

CLS

FOR r=0 TO 20

30

PRINT RND

40

50

NEXT c

REM OUT 32735,32

60

70

CLS

80 FOR r=0 TO 20

90 PRINT

RND

100 NEXT

INKEY$=""

THEN GO TO 10

110

IF

120 OUT 32735,0

```

With screen buffering enabled, the process of printing to the screen becomes invisible to the user. The program still takes the same length of time to output the random numbers but the visual result can be more pleasing to the eye. To terminate the program, hold down any key and the program will end by reverting to the standard display mode.

It may be desirable for a program to adjust its output depending upon whether the new display modes of the SPECTRA interface are available or not. The following program demonstrates how this can be achieved from BASIC:

```

10 OUT 32735,16

20 PRINT "New display modes: ";

30 IF IN 32735<>16 THEN PRINT "not ";

40 PRINT "available"

50 OUT 32735,0

```

# **CHAPTER**

## Joystick socket

The SPECTRA interface includes a Kempston compatible joystick socket, which is the most widely supported standard by Spectrum games. The socket provides a +5V output allowing it to drive the auto-fire mode found on many popular joysticks. To use the joystick socket, it must first be enabled by setting configuration switch 5 to the *on* position.

If a separate Kempston joystick interface or a peripheral which includes a Kempston joystick socket is used then it is necessary to disable the one built into the SPECTRA interface to prevent a conflict and potential damage to the hardware.

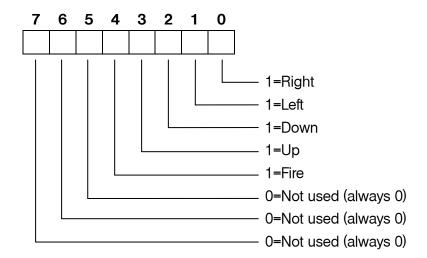

The Kempston joystick socket is read using input port 31 and returns a byte that decodes as follows:

Each joystick direction bit and the fire button bit is set to 1 when its corresponding function is activated. The Kempston standard specifies that the upper 3 bits should always return 0, although it is best not to rely on this since some 3<sup>rd</sup> party Kempston joystick interfaces do not bother to set these bits.

The joystick socket can be read from BASIC using the **IN** function, as the following program demonstrates:

```

10 PRINT AT 0,0; IN 31;" "

20 GOTO 10

```

When the joystick socket is disabled via configuration switch 5, reading the port may return apparently random values instead of the expected value of \$FF (for an idle data bus). It is due to screen bytes appearing on the data bus as a result of the ULA reading the display RAM during construction of the TV picture.

### Chapter 5

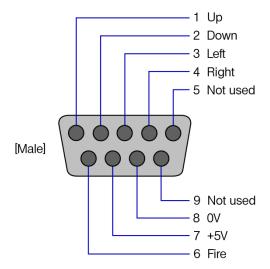

The SPECTRA interface provides a standard male DE-9 joystick socket, which has the following pin-out:

Top view of the SPECTRA joystick socket

# **CHAPTER**

### RS232 socket

The RS232 socket provided by the SPECTRA interface is fully compatible with the RS232 port available on the ZX Interface 1. This means that machine code routines intended to directly drive the ZX Interface 1 RS232 port will operate the SPECTRA RS232 port without the need for modification. In addition, the ROM facilities provided by the SPECTRA interface (see Chapter 7) allow the RS232 port to be controlled directly from BASIC by extending the Spectrum's ROM with a copy of the ZX Interface 1 ROM. It is then possible to open text and binary channels using standard ZX Interface 1 BASIC syntax and hence to run programs originally written to control the ZX Interface 1 RS232 port. The RS232 socket can be used to connect to a range of devices, e.g. a serial printer, a modem, a PC to load/save data. For details on how to control the RS232 port using extended BASIC commands, refer to the ZX Spectrum Microdrive and Interface 1 Manual [2].

To use the RS232 socket, it must be enabled by setting configuration switch 4 to the *on* position. If a ZX Interface 1 is also to be connected then it is necessary to disable the RS232 socket built into the SPECTRA interface to prevent a conflict and potential damage to the hardware.

The RS232 port is capable of transmission speeds up to 19200 baud, and typically sends and receives using 8 data bits, no parity, 2 stop bits and using hardware handshaking (although the format can be different if you write your own custom serial driver routines in machine code).

### Cable wiring

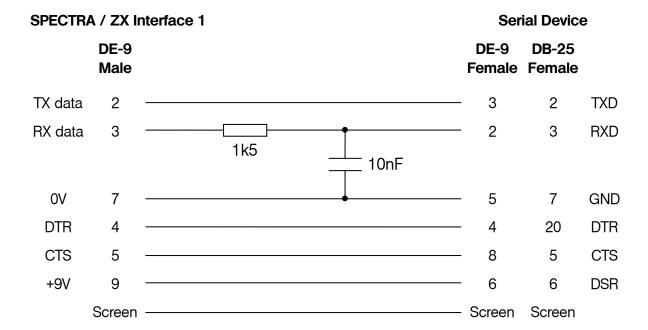

The SPECTRA interface uses a female DE-9 socket for the RS232 port. This is pin compatible with the ZX Interface 1 RS232 socket and has the following pin-out:

Front view of the SPECTRA RS232 socket

A custom cable is required to connect the RS232 socket to a serial device. The wiring needed to connect to a device with a male 9 pin DE-9 connector or a male 25 pin DB-25 connector is shown below.

Wiring of a SPECTRA / ZX Interface 1 RS232 cable

Note that the *screen* connection should be made as this will significantly improve the cable's resilience to interference. A typical RS232 cable may be up to 15m in length.

The cable should include a simple filter circuit consisting of a 1k5 resistor and a 10nF capacitor. Including the filter circuit creates a standard cable design that can be used with the RS232 socket of the ZX Interface 1 as well as that of the SPECTRA interface. The filter circuit is used to minimise the effects of a glitch that occurs on the output data line from the ZX Interface 1 upon every transmission. The glitch occurs because the ZX Interface 1 hardware shares the output data line between the Network ports and the RS232 port and the ROM always reverts back to Network mode after each RS232 transmission. It is this switching action between Network mode and RS232 mode that causes the glitch.

In general, the two devices connected via an RS232 communications link are referred to as the *data terminal equipment* (DTE) and the *data communications equipment* (DCE). Normally the DTE would be viewed as the device that requires sending / receiving of data and the DCE as the device that accepts it or provides it, e.g. a computer would be a DTE and a modem a DCE. The convention is therefore to label of all signals with respect to the DTE. The ZX Interface 1 confusingly labels its RS232 socket pins as if it were a DCE, and hence the *RX data* line is used for sending data and the *TX data* line used for receiving data. The SPECTRA interface adopts the ZX Interface 1 labelling scheme since it reproduces its RS232 functionality.

Note that in RS232, TXD stands for *transmit data*, RXD for *receive data*, DTR for *data terminal ready*, CTS for *clear to send* and DSR for *data set ready*.

### I/O ports

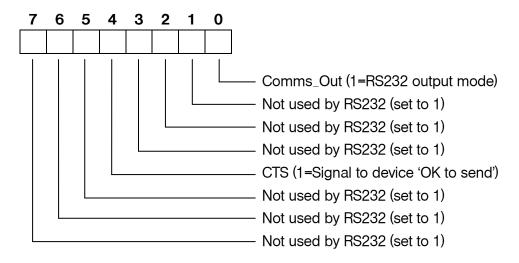

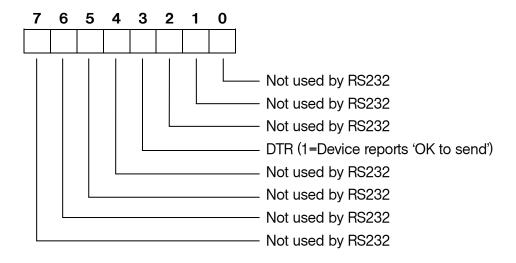

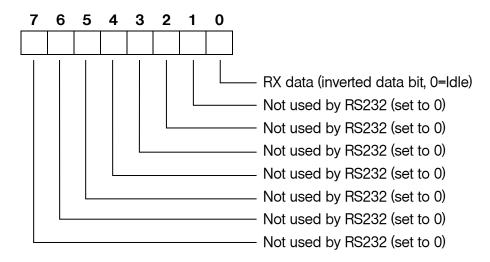

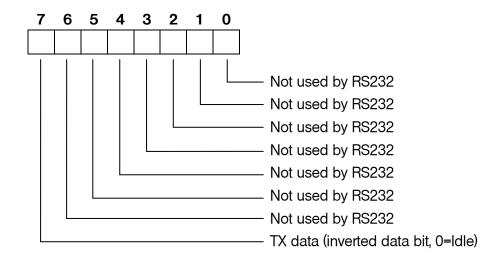

The RS232 socket is software driven using I/O ports 239 and 247. The function of each bit of these ports is shown in the following diagrams. Note that although many of the bits are marked as 'not used' by the RS232 port, they are used on a ZX Interface 1 to control the Network and Microdrives. If a custom serial driver is written in machine code then it is important to set these 'not used' bits as indicated to ensure that the routines will also operate successfully with the ZX Interface 1.

Output port 239 (\$EF = xxx01xxx):

Input port 239 (\$EF = xxx01xxx):

Output port 247 (F7 = xxx10xxx):

Input port 247 (F7 = xxx10xxx):

Note that in order to transmit data on the *RX data* line of the RS232 socket, it is first necessary to set the *Comms\_Out* bit of output port 239. This is required because in a ZX Interface 1 the output circuitry is shared between the Network and RS232. Although there is no network functionality provided by the SPECTRA interface, this mechanism has been reproduced to ensure that its RS232 port operates identically to that found on the ZX Interface 1. The other control signals, *TX data*, *DTR* and *CTS* operate irrespective of the state of the *Comms\_Out* bit. Note also that the *RX data* and *TX data* bits use inverted values, i.e. to send a '1' it is necessary to write a '0' to the *RX data* line and vice versa, and when receiving a '1' the *TX data* line will read in as '0' and vice versa.

RS232 communication performed by the ZX Interface 1 ROM transmits data one byte at a time. Each byte is wrapped with a simple frame to form a packet that consists of a start bit, each data bit (least significant bit first), and finally two stop bits. The transmission duration of each bit lasts for a specific length of time as defined by the baud rate, which dictates the number of bits sent per second. The highest baud rate

possible from the Spectrum is 19200, which equates to a theoretical maximum data rate of 1745 bytes per second. However, in practice a lower rate will always be achieved since it takes time to process the bytes that will be sent and those that are received.

### RS232 operation