SLLS069D - JANUARY 1977 - REVISED APRIL 1998

- High Speed

- Standard Supply Voltage

- Dual Channels

- High Common-Mode Rejection Ratio

- High Input Impedance

- High Input Sensitivity

- Differential Common-Mode Input Voltage Range of ±3 V

- Strobe Inputs for Receiver Selection

- Gate Inputs for Logic Versatility

- TTL Drive Capability

- High dc Noise Margin

- Totem-Pole Outputs

- B Version Has Diode-Protected Input for Power-Off Condition

### description

These circuits are TTL-compatible, high-speed line receivers. Each is a monolithic dual circuit featuring two independent channels. They are designed for general use, as well as for such specific applications as data comparators and balanced, unbalanced, and party-line transmission systems. These devices are unilaterally interchangeable with and are replacements for the SN55107, SN75107, and SN75108, but offer diode-clamped strobe inputs to simplify circuit design.

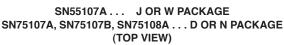

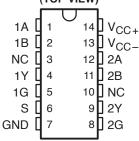

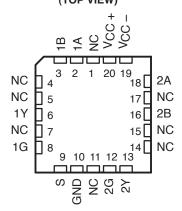

# SN55107A . . . FK PACKAGE (TOP VIEW)

NC - No internal connection

The essential difference between the A and B versions can be seen in the schematics. Input-protection diodes are in series with the collectors of the differential-input transistors of the B versions. These diodes are useful in certain party-line systems that have multiple  $V_{CC+}$  power supplies and can be operated with some of the  $V_{CC+}$  supplies turned off. In such a system, if a supply is turned off and allowed to go to ground, the equivalent input circuit connected to that supply would be as follows:

This would be a problem in specific systems that might have the transmission lines biased to some potential greater than 1.4 V.

The SN55107A is characterized for operation over the full military temperature range of –55°C to 125°C. The SN75107A, SN75107B, and SN75108A are characterized for operation from 0°C to 70°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### **FUNCTION TABLE**

| DIFFERENTIAL INPUTS              | STR | DBES | OUTPUT        |  |

|----------------------------------|-----|------|---------------|--|

| A – B                            | G   | S    | Υ             |  |

| V <sub>ID</sub> ≥ 25 mV          | Х   | Х    | Н             |  |

|                                  | Х   | L    | Н             |  |

| –25 mV < V <sub>ID</sub> < 25 mV | L   | Х    | Н             |  |

|                                  | Н   | Н    | Indeterminate |  |

|                                  | Х   | L    | Н             |  |

| V <sub>ID</sub> ≤ −25 mV         | Ĺ   | Χ    | Н             |  |

|                                  | Н   | Н    | L             |  |

H = high level, L = low level, X = irrelevant

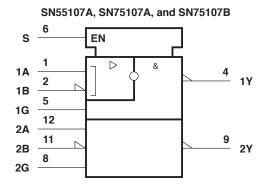

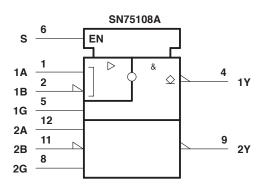

## logic symbol†

$<sup>\</sup>dagger$  These symbols are in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for the D, J, N, and W packages.

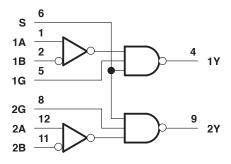

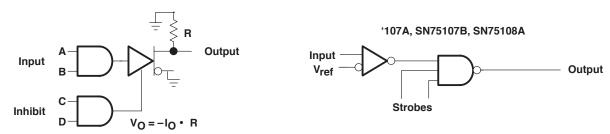

## logic diagram (positive logic)

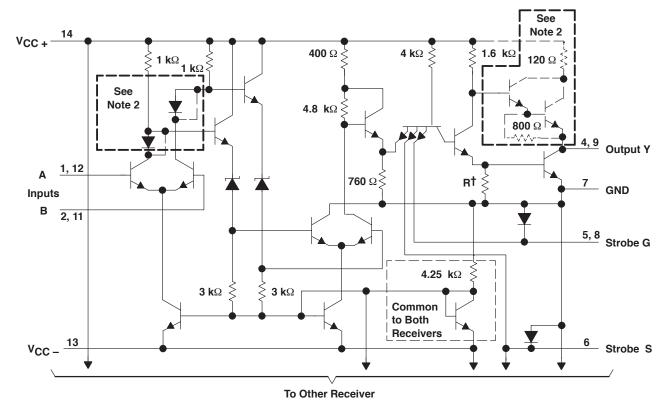

## schematic (each receiver)

Pin numbers shown are for D, J, N, and W packages.

$^{\dagger}\,\text{R}$  = 1 k $\Omega$  for '107A and SN75107B, 750  $\Omega$  for SN75108A.

NOTES: 1. Resistor values shown are nominal.

2. Components shown with dashed lines in the output circuitry are applicable to the '107A and SN75107B only. Diodes in series with the collectors of the differential input transistors are short circuited on '107A and SN75108A.

## SN55107A, SN75107A, SN75107B, SN75108A **DUAL LINE RECEIVERS**

SLLS069D - JANUARY 1977 - REVISED APRIL 1998

## absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Supply voltage, V <sub>CC+</sub> (see Note 3)                        | 7 V                          |

|----------------------------------------------------------------------|------------------------------|

| Supply voltage, V <sub>CC</sub>                                      |                              |

| Differential input voltage, V <sub>ID</sub> (see Note 4)             | ±6 V                         |

| Common-mode input voltage, V <sub>IC</sub> (see Note 5)              | ±5 V                         |

| Strobe input voltage                                                 | 5.5 V                        |

| Continuous total dissipation                                         | See Dissipation Rating Table |

| Storage temperature range, T <sub>stq</sub>                          | 65°C to 150°C                |

| Case temperature for 60 seconds, T <sub>c</sub> : FK package         | 260°C                        |

| Lead temperature 1,6 mm (1/16 inch) from case for 60 seconds: J page | ckage 300°C                  |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: D, N   | I. or W package 260°C        |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 3. All voltage values, except differential voltages, are with respect to network ground terminal.

- 4. Differential voltage values are at the noninverting (A) terminal with respect to the inverting (B) terminal.

- 5. Common-mode input voltage is the average of the voltages at the A and B inputs.

#### **DISSIPATION RATING TABLE**

| PACKAGE | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |

|---------|---------------------------------------|------------------------------------------------|---------------------------------------|----------------------------------------|

| D       | 950 mW                                | 7.6 mW/°C                                      | 608 mW                                | _                                      |

| FK      | 1375 mW                               | 11.0 mW/°C                                     | 880 mW                                | 275 mW                                 |

| J       | 1375 mW                               | 11.0 mW/°C                                     | 880 mW                                | 275 mW                                 |

| N       | 1150 mW                               | 9.2 mW/°C                                      | 736 mW                                | _                                      |

| W       | 1000 mW                               | 8.0 mW/°C                                      | 640 mW                                | 200 mW                                 |

## recommended operating conditions (see Note 6)

|                                                                                     |       | SN55107A |        | SN7510 | UNIT |        |    |

|-------------------------------------------------------------------------------------|-------|----------|--------|--------|------|--------|----|

|                                                                                     | MIN   | NOM      | MAX    | MIN    | NOM  | MAX    |    |

| Supply voltage, V <sub>CC+</sub>                                                    | 4.5   | 5        | 5.5    | 4.75   | 5    | 5.25   | V  |

| Supply voltage, V <sub>CC</sub> _                                                   | -4.5  | -5       | -5.5   | -4.75  | -5   | -5.25  | V  |

| High-level input voltage between differential inputs, V <sub>IDH</sub> (see Note 7) | 0.025 |          | 5      | 0.025  |      | 5      | V  |

| Low-level input voltage between differential inputs, V <sub>IDL</sub> (see Note 7)  | -5‡   |          | -0.025 | -5‡    |      | -0.025 | V  |

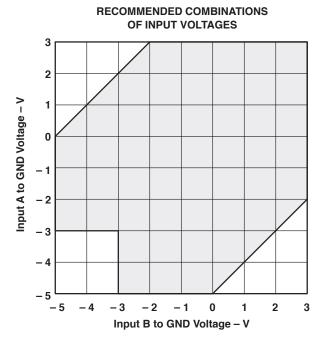

| Common-mode input voltage, V <sub>IC</sub> (see Notes 7 and 8)                      | -3‡   |          | 3      | -3‡    |      | 3      | V  |

| Input voltage, any differential input to GND (see Note 8)                           | -5‡   |          | 3      | -5‡    |      | 3      | V  |

| High-level input voltage at strobe inputs, V <sub>IH(S)</sub>                       | 2     |          | 5.5    | 2      |      | 5.5    | V  |

| Low-level input voltage at strobe inputs, V <sub>IL(S)</sub>                        | 0     |          | 0.8    | 0      |      | 0.8    | V  |

| Low-level output current, IOL                                                       |       |          | -16    |        |      | -16    | mA |

| Operating free-air temperature, T <sub>A</sub>                                      | -55   |          | 125    | 0      |      | 70     | °C |

<sup>‡</sup>The algebraic convention, in which the less positive (more negative) limit is designated as minimum, is used in this data sheet for input voltage levels only.

- NOTES: 6. When using only one channel of the line receiver, the strobe input (G) of the unused channel should be grounded and at least one of the differential inputs of the unused receiver should be terminated at some voltage between -3 V and 3 V.

- 7. The recommended combinations of input voltages fall within the shaded area in Figure 1.

- 8. The common-mode voltage may be as low as -4 V provided that the more positive of the two inputs is not more negative than -3 V

SLLS069D - JANUARY 1977 - REVISED APRIL 1998

NOTE A: Recommended input-voltage combinations are in the shaded area.

Figure 1. Recommended Combinations of Input Voltages

## SN55107A, SN75107A, SN75107B, SN75108A **DUAL LINE RECEIVERS**

SLLS069D - JANUARY 1977 - REVISED APRIL 1998

## electrical characteristics over recommended free-air temperature range (unless otherwise noted)

| DADAMETED                         |                                                   | TEST CONDITIONS <sup>†</sup> |                                                                                     | '107 <i>A</i>                                                | A, SN751 | 07B  | SN75108A |      |      |      |    |

|-----------------------------------|---------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------|----------|------|----------|------|------|------|----|

|                                   | PARAMETER TEST CONDITION                          |                              | DITIONS                                                                             | MIN                                                          | TYP‡     | MAX  | MIN      | TYP‡ | MAX  | UNIT |    |

| VOH                               | High-level output voltage                         |                              | $V_{CC\pm} = MIN,$<br>$V_{IDH} = 25 \text{ mV},$<br>$V_{IC} = -3 \text{ V to 3 V}$  | $V_{IL(S)} = 0.8 \text{ V},$<br>$I_{OH} = -400 \mu\text{A},$ | 2.4      |      |          |      |      |      | ٧  |

| V <sub>OL</sub>                   | Low-level output voltage                          |                              | $V_{CC\pm} = MIN,$<br>$V_{IDL} = -25 \text{ mV},$<br>$V_{IC} = -3 \text{ V to 3 V}$ | $V_{IH(S)} = 2 V$ ,<br>$I_{OL} = 16 \text{ mA}$ ,            |          |      | 0.4      |      |      | 0.4  | ٧  |

| 1                                 | High-level input current                          | Α                            | V <sub>CC±</sub> = MAX                                                              | V <sub>ID</sub> = 5 V                                        |          | 30   | 75       |      | 30   | 75   | μΑ |

| ΊΗ                                | r light-level input current                       | В                            | ACC = - INIXX                                                                       | $V_{ID} = -5 V$                                              |          | 30   | 75       |      | 30   | 75   | μΑ |

| l                                 | Low-level input current                           | Α                            | V00 - MAY                                                                           | $V_{ID} = -5 V$                                              |          |      | -10      |      |      | -10  | uΑ |

| 'IL                               | IIL 2511 15151 Impar sarroin                      | В                            | $V_{CC\pm} = MAX$ $V_I$                                                             | V <sub>ID</sub> = 5 V                                        |          |      | -10      |      |      | -10  | μΑ |

| 1                                 | High-level input current into                     |                              | $V_{CC\pm} = MAX$ ,                                                                 | V <sub>IH(G)</sub> = 2.4 V                                   |          |      | 40       |      |      | 40   | μΑ |

| ΊΗ                                | 1G or 2G                                          |                              | $V_{CC\pm} = MAX, V_{IH(G)} = MAX V_{CC\pm}$                                        |                                                              |          |      | 1        |      |      | 1    | mA |

| IIL                               | Low-level input current into 1G or 2G             |                              | V <sub>CC±</sub> = MAX,                                                             | V <sub>IL(G)</sub> = 0.4 V                                   |          |      | -1.6     |      |      | -1.6 | mA |

|                                   | High-level input current int                      | ~ 6                          | $V_{CC\pm} = MAX$ ,                                                                 | V <sub>IH(S)</sub> = 2.4 V                                   |          |      | 80       |      |      | 80   | μΑ |

| IH                                | nigri-level input current int                     | 03                           | V <sub>CC±</sub> = MAX, V <sub>IH</sub>                                             | (S) = MAX V <sub>CC+</sub>                                   |          |      | 2        |      |      | 2    | mA |

| IIL                               | Low-level input current into                      | o S                          | $V_{CC\pm} = MAX$ ,                                                                 | V <sub>IL(S)</sub> = 0.4 V                                   |          |      | -3.2     |      |      | -3.2 | mA |

| ЮН                                | IOH High-level output current                     |                              | V <sub>CC±</sub> = MIN, V <sub>OH</sub>                                             | = MAX V <sub>CC+</sub>                                       |          |      |          |      |      | 250  | μΑ |

| IOS Short-circuit output current§ |                                                   | $V_{CC\pm} = MAX$            |                                                                                     | -18                                                          |          | -70  |          |      |      | mA   |    |

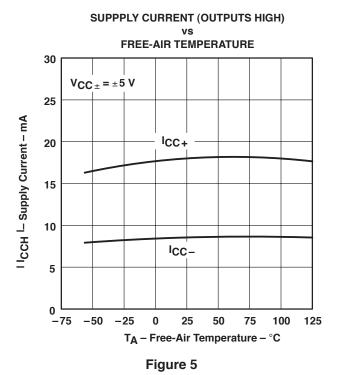

| ICCH+                             | Supply current from V <sub>CC+</sub> outputs high | -,                           | V <sub>CC±</sub> = MAX,                                                             | T <sub>A</sub> = 25°C                                        |          | 18   | 30       |      | 18   | 30   | mA |

| ICCH-                             | Supply current from V <sub>CC</sub> outputs high  | -,                           | $V_{CC\pm} = MAX$ ,                                                                 | T <sub>A</sub> = 25°C                                        |          | -8.4 | -15      |      | -8.4 | -15  | mA |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

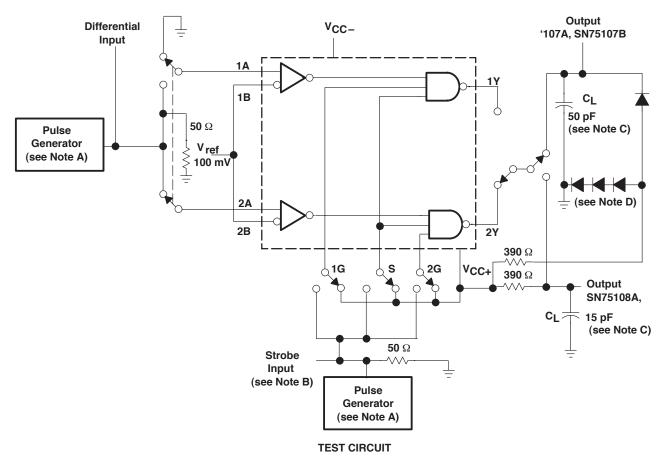

## switching characteristics, V<sub>CC $_{\pm}$ </sub> = $_{\pm}5$ V, T<sub>A</sub> = 25°C, R<sub>L</sub> = 390 $\Omega$ (see Figure 2)

| PARAMETER                                       |                                                    | TEST                   | '107A | , SN751 | 07B | SI  | N75108A | A   | UNIT |

|-------------------------------------------------|----------------------------------------------------|------------------------|-------|---------|-----|-----|---------|-----|------|

|                                                 | PARAMETER                                          |                        | MIN   | TYP     | MAX | MIN | TYP     | MAX | ONIT |

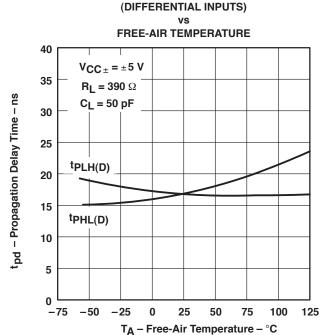

| t=                                              | Propagation delay time, low- to high-level output, | C <sub>L</sub> = 50 pF |       | 17      | 25  |     |         |     | no   |

| IPLH(D)                                         | tPLH(D) from differential inputs A and B           |                        |       |         |     |     | 19      | 25  | ns   |

| t                                               | Propagation delay time, high- to low-level output, |                        |       | 17      | 25  |     |         |     | ns   |

| tPHL(D) from differential inputs A and B        |                                                    | C <sub>L</sub> = 15 pF |       |         |     |     | 19      | 25  | 115  |

| toures                                          | Propagation delay time, low- to high-level output, | C <sub>L</sub> = 50 pF |       | 10      | 15  |     |         |     | ns   |

| tPLH(S) from strobe input G or S                |                                                    | C <sub>L</sub> = 15 pF |       |         |     |     | 13      | 20  | 115  |

| Propagation delay time, high- to low-level outp |                                                    | $C_L = 50 pF$          |       | 8       | 15  |     |         |     | ns   |

| tPHL(S)                                         | from strobe input G or S                           | C <sub>L</sub> = 15 pF |       |         |     |     | 13      | 20  | 115  |

$<sup>\</sup>ddagger$  All typical values are at V<sub>CC+</sub> = 5 V, V<sub>CC-</sub> = -5 V, T<sub>A</sub> = 25°C. § Not more than one output should be shorted at a time.

#### PARAMETER MEASUREMENT INFORMATION

- NOTES: A. The pulse generators have the following characteristics:  $Z_0 = 50 \Omega$ ,  $t_f = 10 \pm 5$  ns,  $t_f = 10 \pm 5$  ns,  $t_{pd1} = 500$  ns, PRR  $\leq 1$  MHz,  $t_{pd2}$  = 1  $\mu$ s, PRR  $\leq$  500 kHz. B. Strobe input pulse is applied to Strobe 1G when inputs 1A-1B are being tested, to Strobe S when inputs 1A-1B or 2A-2B are being

- tested, and to Strobe 2G when inputs 2A-2B are being tested.

- C. C<sub>L</sub> includes probe and jig capacitance.

- D. All diodes are 1N916.

Figure 2. Test Circuit and Voltage Waveforms

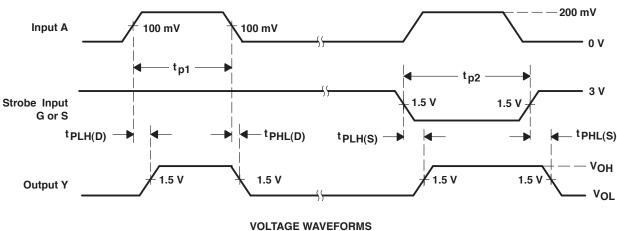

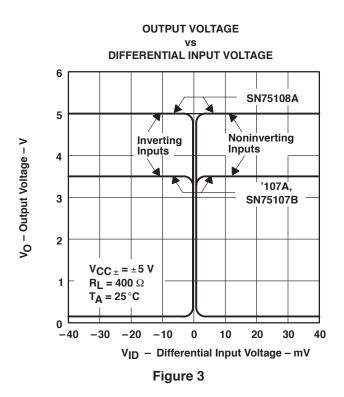

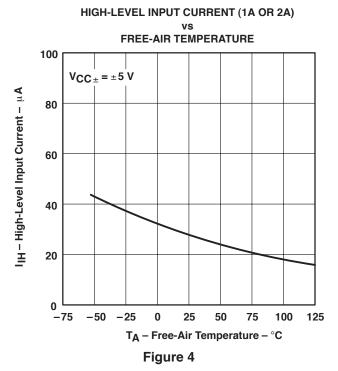

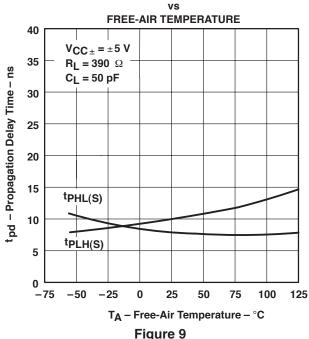

#### TYPICAL CHARACTERISTICS<sup>†</sup>

Figure 6

PROPAGATION DELAY TIME

† Values below 0°C and above 70°C apply to SN55107A only.

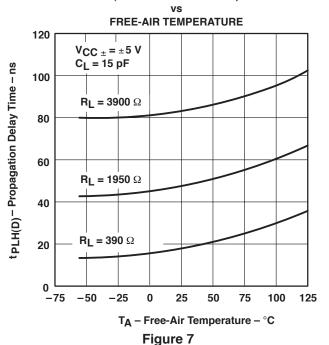

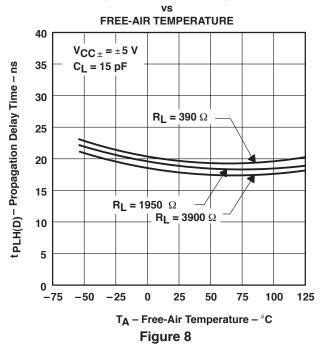

## TYPICAL CHARACTERISTICS†

# PROPAGATION DELAY TIME (LOW-TO-HIGH LEVEL) (DIFFERENTIAL INPUTS)

# PROPAGATION DELAY TIME (LOW-TO-HIGH LEVEL) (DIFFERENTIAL INPUTS)

# SN75108A PROPAGATION DELAY TIME (STROBE INPUTS)

SN75108A

PROPAGATION DELAY TIME (STROBE INPUTS)

† Values below 0°C and above 70°C apply to SN55107A only.

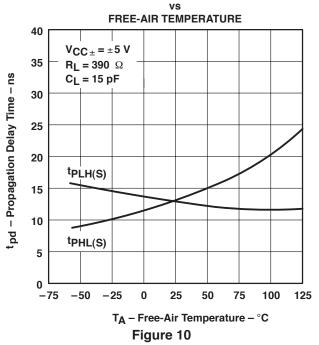

## basic balanced-line transmission system

The '107A, SN75107B, and SN75108A dual line devices are designed specifically for use in high-speed data-transmission systems that utilize balanced terminated transmission lines, such as twisted-pair lines. The system operates in the balanced mode, so noise induced on one line is also induced on the other. The noise appears common mode at the receiver input terminals, where it is rejected. The ground connection between the line driver and receiver is not part of the signal circuit; therefore, system performance is not affected by circulating ground currents.

The unique driver-output circuit allows terminated transmission lines to be driven at normal line impedances. High-speed system operation is ensured because line reflections are virtually eliminated when terminated lines are used. Crosstalk is minimized by low signal amplitudes and low line impedances.

The typical data delay in a system is approximately 30 + 1.3 L ns, where L is the distance in feet separating the driver and receiver. This delay includes one gate delay in both the driver and receiver.

Data is impressed on the balanced-line system by unbalancing the line voltages with the driver output current. The driven line is selected by appropriate driver-input logic levels. The voltage difference is approximately:

$$V_{DIFF} \approx 1/2I_{O(on)} \cdot R_{T}$$

High series line resistance causes degradation of the signal. However, the receivers detect signals as low as 25 mV. For normal line resistances, data can be recovered from lines of several thousand feet in length.

Line-termination resistors  $(R_T)$  are required only at the extreme ends of the line. For short lines, termination resistors at the receiver only may be adequate. The signal amplitude is then approximately:

Figure 11. Typical Differential Data Line

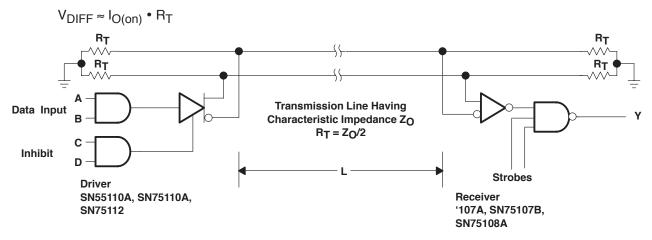

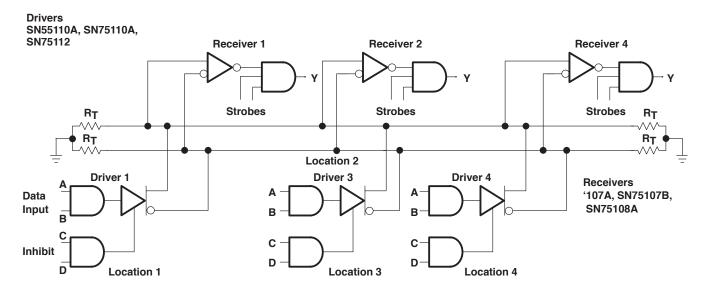

#### data-bus or party-line system

The strobe feature of the receivers and the inhibit feature of the drivers allow these dual line devices to be used in data-bus or party-line systems. In these applications, several drivers and receivers can share a common transmission line. An enabled driver transmits data to all enabled receivers on the line while other drivers and receivers are disabled. Data is time multiplexed on the transmission line. The device specifications allow widely varying thermal and electrical environments at the various driver and receiver locations. The data-bus system offers maximum performance at minimum cost.

Figure 12. Typical Differential Party Line

### unbalanced or single-line systems

These dual line circuits also can be used in unbalanced or single-line systems. Although these systems do not offer the same performance as balanced systems for long lines, they are adequate for very short lines where environmental noise is not severe.

The receiver threshold level is established by applying a dc reference voltage to one receiver input terminal. The signal from the transmission line is applied to the remaining input. The reference voltage should be optimized so that signal swing is symmetrical about it for maximum noise margin. The reference voltage should be in the range of -3 V to 3 V. It can be provided by a voltage supply or by a voltage divider from an available supply voltage.

A single-ended output from a driver can be used in single-line systems. Coaxial or shielded line is preferred for minimum noise and crosstalk problems. For large signal swings, the high output current (typically 27 mA) of the SN75112 is recommended. Drivers can be paralleled for higher current. When using only one channel of the line drivers, the other channel should be inhibited and/or have its outputs grounded.

#### SN55110A, SN75110A, SN75112

Figure 13. Single-Ended Operation

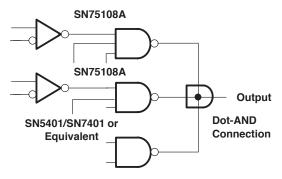

## SN75108A dot-AND output connections

The SN75108A line receiver features an open-collector-output circuit that can be connected in the dot-AND logic configuration with other similar open-collector outputs. This allows a level of logic to be implemented without additional logic delay.

Figure 14. Dot-AND Connection

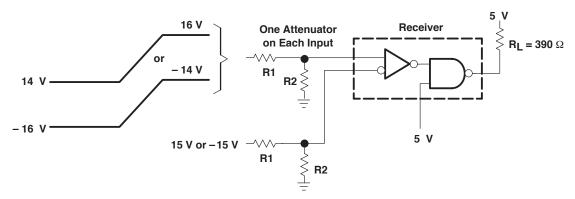

#### increasing common-mode input voltage range of receiver

The common-mode voltage range (CMVR) is defined as the range of voltage applied simultaneously to both input terminals that, if exceeded, does not allow normal operation of the receiver.

The recommended operating CMVR is  $\pm 3$  V, making it useful in all but the noisiest environments. In extremely noisy environments, common-mode voltage can easily reach  $\pm 10$  V to  $\pm 15$  V if some precautions are not taken to reduce ground and power supply noise, as well as crosstalk problems. When the receiver must operate in such conditions, input attenuators should be used to decrease the system common-mode noise to a tolerable level at the receiver inputs. Differential noise is also reduced by the same ratio. These attenuators were omitted intentionally from the receiver input terminals so the designer can select resistors that are compatible with his particular application or environment. Furthermore, the use of attenuators adversely affects the input sensitivity, the propagation delay time, the power dissipation, and in some cases (depending on the selected resistor values) the input impedance; thereby reducing the versatility of the receiver.

The ability of the receiver to operate with approximately  $\pm 15$  V common-mode voltage at the inputs has been checked using the circuit shown in Figure 15. Resistors R1 and R2 provide a voltage-divider network. Dividers with three different values presenting a 5-to-1 attenuation were used to operate the differential inputs at approximately  $\pm 3$  V common-mode voltage. Careful matching of the two attenuators is needed to balance the overdrive at the input stage. The resistors used are shown in Table 1.

#### Table 1

| Attenuator 1: | $R1 = 2 k\Omega$ ,   | $R2 = 0.5 \text{ k}\Omega$ |

|---------------|----------------------|----------------------------|

| Attenuator 2: | $R1 = 6 k\Omega$ ,   | $R2 = 1.5 \text{ k}\Omega$ |

| Attenuator 3: | R1 = 12 k $\Omega$ , | $R2 = 3 k\Omega$           |

## increasing common-mode input voltage range of receiver (continued)

Table 2 shows some of the typical switching results obtained under such conditions.

Table 2. Typical Propagation Delays for Receiver With Attenuator Test Circuit Shown in Figure 15

| DEVICE   | PARAMETERS       | INPUT<br>ATTENUATOR | TYPICAL (NS) |

|----------|------------------|---------------------|--------------|

|          |                  | 1                   | 20           |

|          | <sup>t</sup> PLH | 2                   | 32           |

| '107A    |                  | 3                   | 42           |

| SN75107B |                  | 1                   | 22           |

|          | <sup>t</sup> PHL | 2                   | 31           |

|          |                  | 3                   | 33           |

|          |                  | 1                   | 36           |

| SN75108A | t <sub>PLH</sub> | 2                   | 47           |

|          |                  | 3                   | 57           |

|          |                  | 1                   | 29           |

|          | <sup>t</sup> PHL | 2                   | 38           |

|          |                  | 3                   | 41           |

Figure 15. Common-Mode Circuit for Testing Input Attenuators With Results Shown in Table 2

SLLS069D - JANUARY 1977 - REVISED APRIL 1998

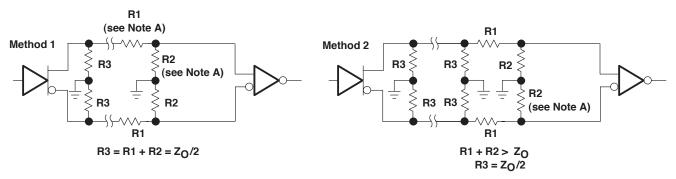

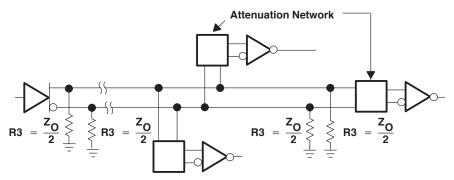

Two methods of terminating a transmission line to reduce reflections are shown in Figure 16. The first method uses the resistors as the attenuation network and line termination. The second method uses two additional resistors for the line terminations.

#### APPLICATION INFORMATION

NOTE A: To minimize the loading, the values of R1 and R2 should be fairly large. Examples of possible values are shown in Table 1.

#### Figure 16. Termination Techniques

For party-line operation, method 2 should be used as shown in Figure 17.

Figure 17. Party-Line Termination Technique

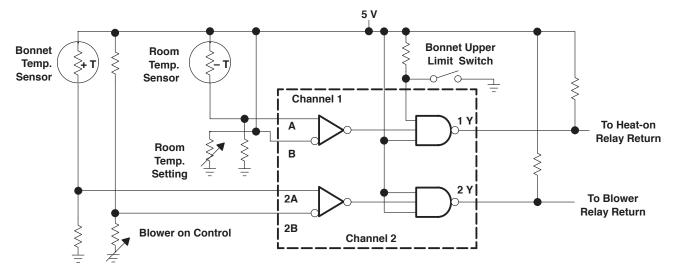

## furnace control using the SN75108A

The furnace control circuit in Figure 18 is an example of the possible use of the SN75108A series in areas other than what would normally be considered electronic systems. A description of the operation of this control follows. When the room temperature is below the desired level, the resistance of the room temperature sensor is high and channel 1 noninverting input is below (less positive than) the reference level set on the input differential amplifier. This situation causes a low output, operating the heat-on relay and turning on the heat. The channel 2 noninverting input is below the reference level when the bonnet temperature of the furnace reaches the desired level. This causes a low output, thus operating the blower relay. Normally the furnace is shut down when the room temperature reaches the desired level and the channel 1 output goes high, turning the heat off. The blower remains on as long as the bonnet temperature is high, even after the heat-on relay is off. There is also a safety switch in the bonnet that shuts down the furnace if the temperature there exceeds desired limits. The types of temperature-sensing devices and bias-resistor values used are determined by the particular operating conditions encountered.

Figure 18. Furnace Control Using SN75108A

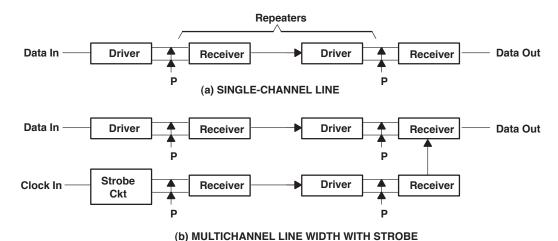

#### repeaters for long lines

In some cases, the driven line may be so long that the noise level on the line reaches the common-mode limits or the attenuation becomes too large and results in poor reception. In such a case, a simple application of a receiver and a driver as repeaters [shown in Figure 19(a)] restores the signal level and allows an adequate signal level at the receiving end. If multichannel operation is desired, then proper gating for each channel must be sent through the repeater station using another repeater set as in Figure 19(b).

Figure 19. Receiver-Driver Repeaters

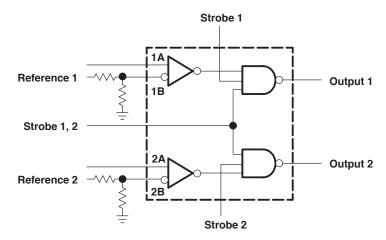

#### receiver as dual differential comparator

There are many applications for differential comparators, such as voltage comparison, threshold detection, controlled Schmitt triggering, and pulse-width control.

As a differential comparator, a '107A or SN75108A can be connected to compare the noninverting input terminal with the inverting input as shown in Figure 20. The output is high or low, resulting from the A input being greater or less than the reference. The strobe inputs allow additional control over the circuit so that either output, or both, can be inhibited.

Figure 20. SN75107A Series Receiver as a Dual Differential Comparator

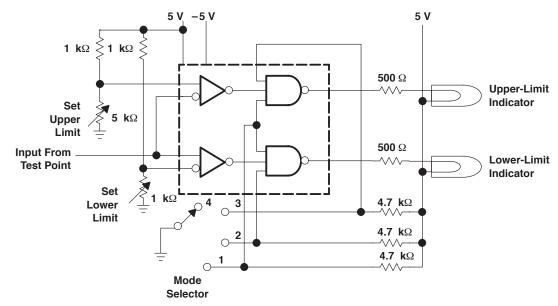

#### window detector

The window detector circuit in Figure 21 has a large number of applications in test equipment and in determining upper limits, lower limits, or both at the same time, such as detecting whether a voltage or signal has exceeded its window limits. Illumination of the upper-limit (lower-limit) indicator shows that the input voltage is above (below) the selected upper (lower) limit. A mode selector is provided for selecting the desired test. For window detecting, the upper-and-lower-limits test position is used.

#### MODE SELECTOR LEGEND

| POSITION | CONDITION                       |

|----------|---------------------------------|

| 1        | Off                             |

| 2        | Test for Upper Limit            |

| 3        | Test for Lower Limit            |

| 4        | Test for Upper and Lower Limits |

Figure 21. Window Detector Using SN75108A

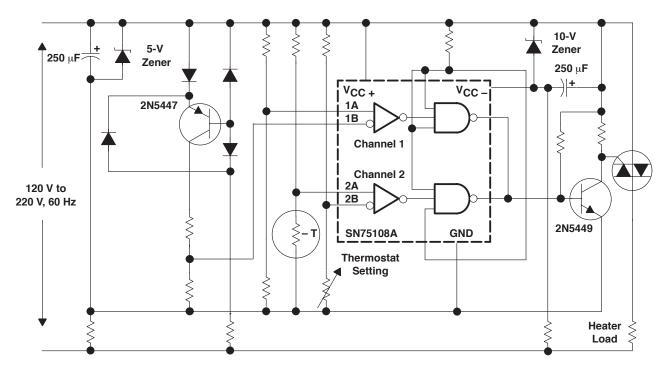

#### temperature controller with zero-voltage switching

The circuit in Figure 22 switches an electric-resistive heater on or off by providing negative-going pulses to the gate of a triac during the time interval when the line voltage is passing through zero. The pulse generator is the 2N5447 and four diodes. This portion of the circuit provides negative-going pulses during the short time (approximately 100  $\mu$ s) when the line voltage is near zero. These pulses are fed to the inverting input of one channel of the SN75108A. If the room temperature is below the desired level, the resistance of the thermistor is high and the noninverting input of channel 2 is above the reference level determined by the thermostat setting. This provides a high-level output from channel 2. This output is ANDed with the positive-going pulses from the output of channel 1, which are reinverted in the 2N5449.

Figure 22. Zero-Voltage Switching Temperature Controller

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated